Voor mensen die niet de CPU kopen voor gaming maar voor andere software, voor longevity, om voldoende extra waarde te bieden t.o.v. Intel, om software te pushen om meer kernen te gebruiken (want Intel zal proberen om hierin mee te gaan), omdat je je product stack naar boven toe kan uitbreiden (met een 3800X die je voor meer winst kan verkopen en die heus wel verkocht zal worden) en omdat het qua vermogen goed te doen is. Heeft AMD niet al minstens de laatste 10-15 jaar gespeculeerd dat de software vanzelf wel volgt als de hardware meer kernen bevat? Juist met zoveel kernen maakt AMD het Intel moeilijk want hoe groter het aantal kernen hoe minder competitief Intel is en bij het overschakelen naar mutli-die CPU's zal Intel beginnen met een achterstand.DaniëlWW2 schreef op vrijdag 16 november 2018 @ 11:54:

Verder vraag ik me af waarom AMD precies voorbij de 8c moet gaan?

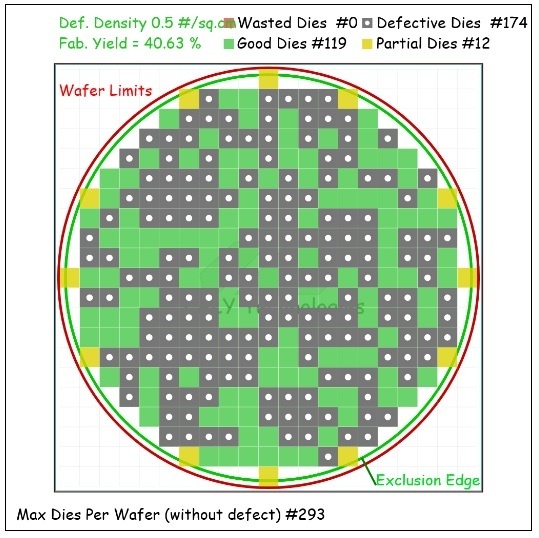

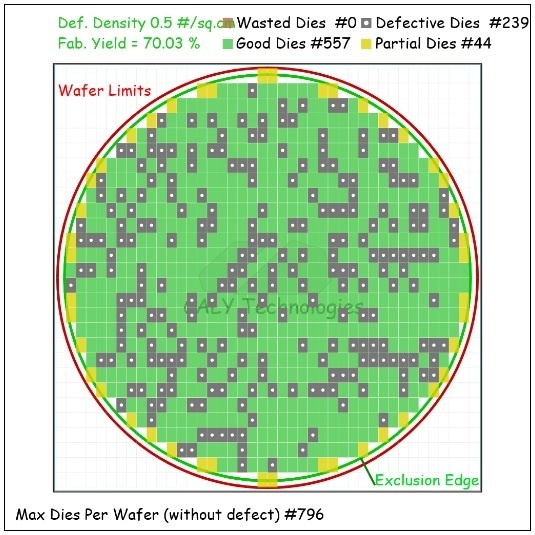

"kosten fors opdrijven": als er meer waarde is dan kan je het voor een hogere prijs verkopen en het hangt ook maar af van hoe AMD het uitvoert. Als ze bijvoorbeeld beschadigde stukjes die niet goed genoeg zijn voor Epyc en TR gebruiken dan kan het reuze meevallen met de kosten hoewel de yields inderdaad goed genoeg zouden moeten zijn dat dit wellicht onvoldoende is. Als ze aparte dies met 6 kernen per CCX gebruiken dan valt het reuze mee met de kosten: dan zit je op ongeveer 3/4de van het oppervlakte waardoor je minstens voor 50% de hogere kosten per vierkante micrometer voor TSMC 7 nm. zou compenseren. De extra kosten zitten dan in het maken van de mask.

"Meerdere goed geïnformeerde mensen" hebben WCCFTech laten weten dat Ryzen 3 "12 tot 16 kernen" zou bevatten "maar waarschijnlijk niet meer dan 12". Als WCCFTech er nu vaak naast had gezeten dan zou ik dit met een hele grove korrel zout nemen maar WCCFTech heeft bij Ryzen tot nu toe altijd gelijk gekregen bij alles wat ze lekten over Zen en dat zijn inmiddels aardig wat leaks. Ik ken hun reputatie maar ik ga af op hun track record voor Zen, die is best wel goed.

[ Voor 16% gewijzigd door Verwijderd op 16-11-2018 14:17 ]

:strip_exif()/i/2007025992.png?f=thumbmini)

:strip_exif()/i/2005553786.png?f=thumbmini)

:strip_exif()/i/2004983538.png?f=thumbmini)

:strip_exif()/i/2006261514.webp?f=thumbmini)

:fill(white):strip_exif()/i/2005466442.jpeg?f=thumbmini)

:fill(white):strip_exif()/i/2003532750.jpeg?f=thumbmini)

:fill(white):strip_exif()/i/2003937724.jpeg?f=thumbmini)

:fill(white):strip_exif()/i/2003937722.jpeg?f=thumbmini)

:fill(white):strip_exif()/i/2006752498.jpeg?f=thumbmini)

:fill(white):strip_exif()/i/2006752500.jpeg?f=thumbmini)

:fill(white):strip_exif()/i/2005322060.jpeg?f=thumbmini)

:strip_exif()/i/2001936103.png?f=thumbmini)

:strip_exif()/i/2001936107.png?f=thumbmini)

:fill(white):strip_exif()/i/2002872184.jpeg?f=thumbmini)

:fill(white):strip_exif()/i/2004307982.jpeg?f=thumbmini)

:strip_exif()/i/2001936105.png?f=thumbmini)

:fill(white):strip_exif()/i/2001904109.jpeg?f=thumbmini)

:fill(white):strip_exif()/i/2001415763.jpeg?f=thumbmini)

:strip_exif()/i/2001766419.png?f=thumbmini)

:strip_exif()/i/2001457441.png?f=thumbmini)

:strip_exif()/i/2001936109.png?f=thumbmini)

:strip_exif()/i/2002209673.png?f=thumbmini)

:strip_exif()/i/2001469737.png?f=thumbmini)

:fill(white):strip_exif()/i/2002872196.jpeg?f=thumbmini)

:fill(white):strip_exif()/i/2001583647.jpeg?f=thumbmini)

:strip_exif()/i/2001457443.png?f=thumbmini)

:fill(white):strip_exif()/i/2001429879.jpeg?f=thumbmini)

:fill(white):strip_exif()/i/2001583645.jpeg?f=thumbmini)

/u/324913/crop56a24cce05cd3_cropped.png?f=community)

/u/400/defember100.png?f=community)

/u/46804/crop5f989efcbb253.png?f=community)

:strip_icc():strip_exif()/u/83337/countess6-nice.jpg?f=community)

:strip_icc():strip_exif()/u/357407/crop5614c78b48976_cropped.jpeg?f=community)

/u/99328/crop689092bc4e60c_cropped.png?f=community)

:strip_icc():strip_exif()/u/45765/3dfx2.jpg?f=community)

/u/4501/crop5bdb35c450e89.png?f=community)

:strip_icc():strip_exif()/u/16203/linux.jpg?f=community)

/u/137180/TS4YTL60R.png?f=community)

:strip_icc():strip_exif()/u/195118/crop6910ffb546e2c.jpg?f=community)

:strip_icc():strip_exif()/u/889105/crop5c9dd4b7d8191_cropped.jpeg?f=community)

/u/266427/41_2_6060.png?f=community)

:strip_icc():strip_exif()/u/294814/crop5dfccf4b6dfb6_cropped.jpeg?f=community)

:strip_exif()/u/211274/bestabstractwallpapers5.gif?f=community)

:strip_icc():strip_exif()/u/544669/someone%2520is%2520wrong%2520on%2520the%2520internet60.jpg?f=community)

:strip_icc():strip_exif()/u/449315/crop5630ddc30dde8_cropped.jpeg?f=community)