Graphene; a material that can do everything, except leave the lab. - Asianometry

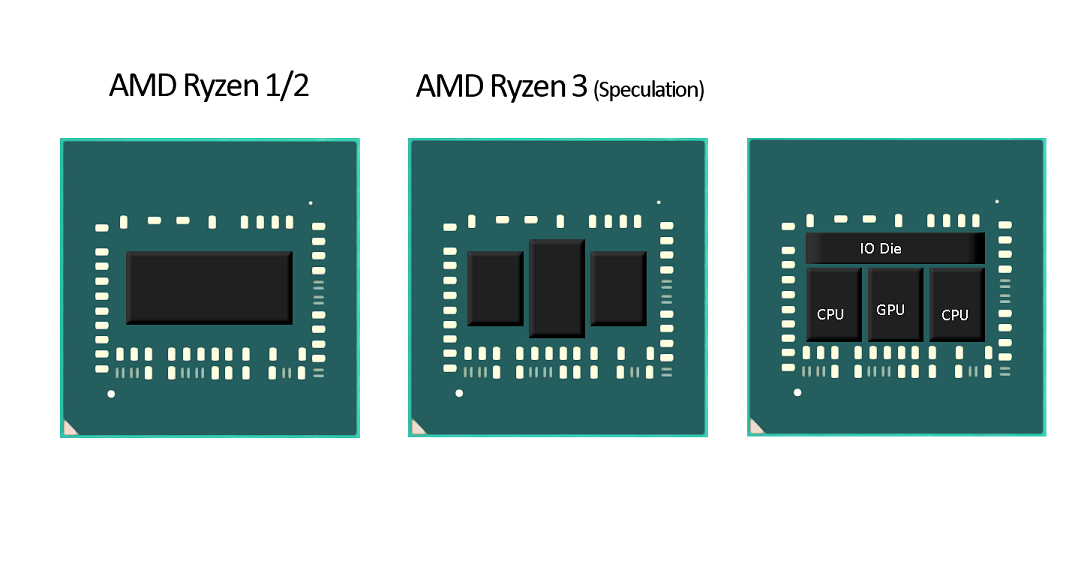

Dat kan nooit dezelfde chip worden, is nl veel te groot en moet wat heatspreading toch ook in balans zijn, je wil de 2 chiplets voor Ryzen (aangenomen dat het 16 cores gaat worden) wel het liefst in het midden van de socket hebben.

Gaat Ryzen3000 2 IO dies krijgen, en dus in een andere vorm ?

En hoe gaat Threadripper eruit zien, kan niet door alle buitenste chips weg te laten, dat zou imho teveel latency opbrengen.(hoewel misschien ook niet)

Ik vind het een apart design, en had de cores meer in een ring en/of meer in het midden verwacht, maar daar zal later wel een goede uitleg voor komen.

Het is nu wel makkelijk om meer cores erbij te plakken.

How do you save a random generator ?

Dat vraag ik me dus ook af. Het kan natuurlijk dat ze een heel ander design voor de desktop hebben maar dat klinkt niet heel erg efficient of logisch.

Ik gok eigenlijk dat er 2 verschillende i/o chips gemaakt zullen worden. Voor Ryzen zie ik dan een aparte (stuk kleinere) i/o chip + 2 chiplets.

Zou heel graag alle topologie info nu alvast hebben

PC Specs

Asus ROG Strix B650E-E | AMD 9800X3D |TR Phantom Spirit 120 SE | G-Skill 32GB DDR5 6000C30 M-die | 4090 FE | LG 3840*1600p 160Hz | Corsair RM1000x Shift

Nee, Ryzen krijgt geen IO chip alleen Epyc. Epyc maakt gebruik van Ryzen die's. Het enige wat nieuw is de 14nm IO voor Epyc.enchion schreef op dinsdag 6 november 2018 @ 21:46:

Wat ik mij ook afvraag, hoe gaat die 14nm IO die eruit zien voor Ryzen.

Dat kan nooit dezelfde chip worden, is nl veel te groot en moet wat heatspreading toch ook in balans zijn, je wil de 2 chiplets voor Ryzen (aangenomen dat het 16 cores gaat worden) wel het liefst in het midden van de socket hebben.

Gaat Ryzen3000 2 IO dies krijgen, en dus in een andere vorm ?

En hoe gaat Threadripper eruit zien, kan niet door alle buitenste chips weg te laten, dat zou imho teveel latency opbrengen.(hoewel misschien ook niet)

Ik vind het een apart design, en had de cores meer in een ring en/of meer in het midden verwacht, maar daar zal later wel een goede uitleg voor komen.

Het is nu wel makkelijk om meer cores erbij te plakken.

Ik had begrepen dat alle IO die in de Ryzen die`s zat juist naar die 14nm uncore die verhuist waren waardoor de ryzen chiplets nog kleiner konden worden.polli_ schreef op dinsdag 6 november 2018 @ 22:02:

[...]

Nee, Ryzen krijgt geen IO chip alleen Epyc. Epyc maakt gebruik van Ryzen die's. Het enige wat nieuw is de 14nm IO voor Epyc.

btw Threadripper3 gaat lijkt mij ook die 14nm uncore die krijgen met memorycontroller erin dus de 2990wx zal de enige cpu zijn die ooit in die layout gewerkt heeft. (met cores zonder MEMcontroller)

How do you save a random generator ?

Knap dat jij dat al weet.polli_ schreef op dinsdag 6 november 2018 @ 22:02:

[...]

Nee, Ryzen krijgt geen IO chip alleen Epyc. Epyc maakt gebruik van Ryzen die's. Het enige wat nieuw is de 14nm IO voor Epyc.

Dat zou overigens betekenen dat er twee verschillende 7nm chiplets gemaakt moeten worden wat mij minder logisch lijkt. Maar het kan wel natuurlijk.

PC Specs

Asus ROG Strix B650E-E | AMD 9800X3D |TR Phantom Spirit 120 SE | G-Skill 32GB DDR5 6000C30 M-die | 4090 FE | LG 3840*1600p 160Hz | Corsair RM1000x Shift

Weten we nu ook waarom TR en Epyc zo'n gigantische socket hebben.

Maar hij is mooi.

In het algemeen lijkt AMD precies te doen met Zen 2 waar ik op hoopte. We hebben:

-Chiplets

-256bit FPU's

-Flink meer L3 cache omdat Zen 1/+ al enige bottleneck lijken te hebben. 2MB per core lijkt niet genoeg te zijn dus we gaan naar 4MB.

-7nm zal zeker helpen met clockspeeds.

Hogere "IPC" mag je denk ik ook wel vanuit gaan. Genoeg aanleiding om het nu al te vermoeden. Nee, dan bedoel ik dus niet 3% zoals Zen naar Zen+.

Never argue with an idiot. He will drag you down to his own level and beat you with experience.

DaniëlWW2 schreef op dinsdag 6 november 2018 @ 22:12:

Weten we nu ook waarom TR en Epyc zo'n gigantische socket hebben.

Maar hij is mooi.

Maw 3x zoveel cores per oppervlak.

De 2 Ryzen chiplets aan elkaar lijken trouwens net zo breed te zijn als de 14nm uncore, dus dat geeft misschien al een idee hoe Ryzen3 eruit gaat zien. (met een 14nm uncore die die 1/4 van de grootte van de Epyc variant is.)

[ Voor 46% gewijzigd door enchion op 06-11-2018 22:41 ]

How do you save a random generator ?

Graphene; a material that can do everything, except leave the lab. - Asianometry

We krijgen waarschijnlijk twee Zen 2 designs. Waarbij een voor consumenten bedoelt is met een on die geintegreerde memory contoller want de huidige AM4 socket(1331 pinnen) is niet compatible met de IO chiplet design.Het verplaatsen van de onboard memory controller naar een off die chip zorgt voor een hele hoge latency penalty.Help!!!! schreef op dinsdag 6 november 2018 @ 22:08:

[...]

Knap dat jij dat al weet.

Dat zou overigens betekenen dat er twee verschillende 7nm chiplets gemaakt moeten worden wat mij minder logisch lijkt. Maar het kan wel natuurlijk.

De andere design is bedoelt voor zakelijke markt en bevat een IO chip met daarop Management/Security Processor, Server Controller Hub, memory controller etc. AMD heeft publiekelijk gezegd dat ROME compatibel is met NAPLES. De SP3 socket(4094 pinnen) is wel compatible met IO chiplet design. En aangezien SP 3 en TR 4 zelfde pin layout hebben geldt dit waarschijnlijk ook voor threadripper.

Ik doelde eigenlijk meer op pin layout.

64c is namelijk vrij extreem.

Never argue with an idiot. He will drag you down to his own level and beat you with experience.

Maw voor Ryzen hebben ze WEL de memorycontroller en PCIE en andere IO op 7nm gemaaktpolli_ schreef op dinsdag 6 november 2018 @ 22:46:

[...]

We krijgen waarschijnlijk twee Zen 2 designs. Waarbij een voor consumenten bedoelt is met een on die geintegreerde memory contoller want de huidige AM4 socket(1331 pinnen) is niet compatible met de IO chiplet design.Het verplaatsen van de onboard memory controller naar een off die chip zorgt voor een hele hoge latency penalty.

De andere design is bedoelt voor zakelijke markt en bevat een IO chip met daarop Management/Security Processor, Server Controller Hub, memory controller etc. AMD heeft publiekelijk gezegd dat ROME compatibel is met NAPLES. De SP3 socket(4094 pinnen) is wel compatible met IO chiplet design. En aangezien SP 3 en TR 4 zelfde pin layout hebben geldt dit waarschijnlijk ook voor threadripper.

En dat vervolgens niet op de Epyc Rome CPU gebruikt.

How do you save a random generator ?

Exact. Over Ryzen is nog niks aangekondigd dus het zou kunnen maar is imo erg onlogisch o.a. om deze reden.enchion schreef op dinsdag 6 november 2018 @ 22:54:

[...]

Maw voor Ryzen hebben ze WEL de memorycontroller en PCIE en andere IO op 7nm gemaakt

En dat vervolgens niet op de Epyc Rome CPU gebruikt.

Er moeten dan 2 verschillende ontwerpen gemaakt en geproduceerd worden op het duurste en meeste schaarse procesnode.

Je profiteert ook niet meer van de eenvoud van het ontwerp / binning.

Nee, ik zie dit niet gebeuren maar het kan wel natuurlijk.

PC Specs

Asus ROG Strix B650E-E | AMD 9800X3D |TR Phantom Spirit 120 SE | G-Skill 32GB DDR5 6000C30 M-die | 4090 FE | LG 3840*1600p 160Hz | Corsair RM1000x Shift

Ik blijf bij mijn standpunt dat als mensen nu geen 2700X boven een 9900K (699 euro in NL) kiezen ze ook geen 3700X boven een 9900K kiezen. Ook als die 3700X in alles beter zou zijn.

AMD gaat nu vol op de datacenter met Epyc 2. Laten we heel optimistisch zeggen dat Intel het voor elkaar krijgt om 10nm processors voor eind 2019 klaar te hebben. Dan zal dat ook eerst datacenter moeten zijn. Daar ligt de grootste markt. En die wil Intel echt niet verliezen. Dus de opvolger van de 9900K laat nog heel lang op zich wachten.

De hoge prijzen mij de consumer processors lang Intel zal daarom ook nog wel effe aanblijven.

AMD doet er goed aan om Zen 2 te optimaliseren (en voor de 3700X misschien al zelfs wat features/verbeteringen van Zen 3 er in te verwerken?). Ik denk dat AMD de ruimte heeft om de launch van Ryzen 3 met drie maanden uit te stellen om bij de reviews slechts enkele procenten meer performance. Het gaat er niet om dat AMD iets heeft om met Intel te concurreren. Het gaat er om dat AMD een processor uitbrengt die de 9900K in alles verslaat om de perceptie van high-end, kwaliteit en performance per watt te verschuiven van Intel naar AMD zelf. Dat is veel belangrijker.

Dat is met Epyc en Threadripper al redelijk gelukt met Zen 1 en Zen +. Nu nog met Ryzen met Zen 2.

Als alleen de moederborden voor Threadripper nog eens goedkoper zouden worden, dan wordt het echt een nobrainer.

How do you save a random generator ?

Verwijderd

vs.

Een bijzaak en het meest triviale eerstewereldprobleem waarvoor 's werelds kleinste viool die vals gestemd staat bespeeld mag worden.

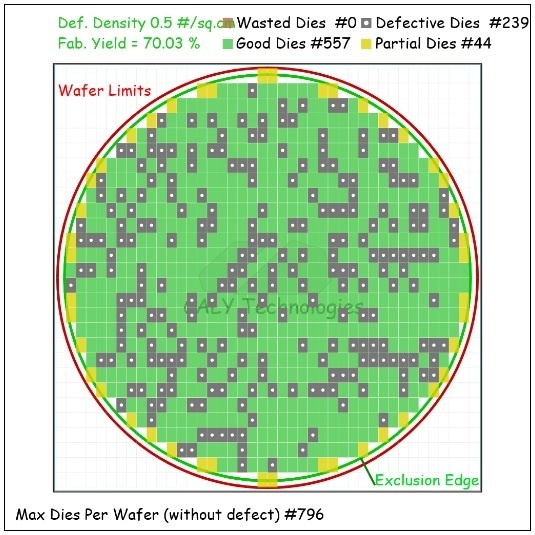

Met twee geheugenkanalen? Dat zou een beetje krap kunnen zijn. De yields zullen wellicht wat lager zijn in welk geval de beschadigde dies (niet 8 werkende kernen) die niet geschikt zijn voor TR/Epyc naar Ryzen gaan.Help!!!! schreef op dinsdag 6 november 2018 @ 21:20:

Ben wel benieuwd wat dit voor de Ryzen betekent. 16 cores naar de desktop lijkt me nu redelijk waarschijnlijk.

Laat AMD en TSMC maar lekker de tijd nemen om het zo goed mogelijk te tweaken. Die ">1,25" spreekt boekdelen. >, omdat ze weten dat het beter gaat worden maar ze niet kunnen inschatten hoeveel het precies omhoog gaat. TSMC sprak over 35% meer performance, AMD over 25%, waar zit het gat? Tweaking van de node? Het verbeteren van het productieproces? Bug in de microcode? ...Van mij mag dit ding morgen naar de desktop komen maar ben bang dat het nog wel zeker tot (ver in) Q2 gaat duren

Over de topologie valt nog niets te zeggen maar een kwart van die middelste chiplet voor Ryzen3 met 2 CCX'en ligt het meest voor de hand want AMD moet extra kernen geven voor Ryzen3 en dus volstaat 1 CCX met 8 kernen niet. Dan is het de vraag of dat ze een CCX met minder kernen hebben gemaakt voor Ryzen of die CCX'en met 8 kernen gebruik in welk geval er ongetwijfeld een hoop stukken met beschadigde kernen bij de hogere segmenten van Ryzen terecht komen.

Dit is wat ik verwacht, rekening houdende met yields (ik speculeer dat die nog niet geweldig zijn): 10 kernen voor de 3600(X), 12 kernen voor de 3700(X), misschien 14 kernen voor een 3800(X). Misschien een 3900X of zo met 16 kernen maar dan zit je wel met het probleem dat je slechts twee geheugenkanalen hebt.

Het uitbreiden van de product-stack met meer marges voor betere producten zal AMD ongetwijfeld interessant vinden, dit deden ze immers voor Threadripper (van $1000 naar $1800 maar ook meer kernen en zo).

Dit sluit aan bij de geruchten die er al waren, ze spraken toen over 10 en 12 kernen met de kanttekening om "niet op 12 te rekenen". Echter weten we nu dat de node het beter doet dan verwacht waarbij niet werd gespecificeerd hoe precies die node het beter zou doen dan verwacht.

Overigens wordt minstens 15% 'IPC' genoemd, het is al van 10-12% naar 15% gegaan met wat tweaken. Volgens Chiphell zal de memorycontroller ook veel beter zijn (snelheid en latency).

Die zullen inderdaad een iets grotere latency hebben, dat kan je niet voorkomen.Ben wel benieuwd hoe dit nu gaat werken qua chiplet latency. De buitenste chiplets zitten veel verder van de I/O chip af...

Mogelijk (het zou niet onlogisch zijn om dat gelijk te willen hebben) maar dan heb je in totaal dus wel een grotere latency doordat die buitenste dies er ook zitten. Een klein offer wat de moeite waard is maar die extra latency is er in ieder geval.NitroX infinity schreef op dinsdag 6 november 2018 @ 21:33:

[...]

Die buitenste hebben waarschijnlijk directe paden naar de i/o chip en die binnenste gaan er met een paar bochtjes naartoe om de lengte van de paden gelijk te houden.

Edit

Inmiddels heeft AMD wel heel de presentatie online gezet met professioneel geluid en beeld.

[ Voor 45% gewijzigd door Verwijderd op 07-11-2018 16:52 ]

Maar zou 16 cores icm mogelijk hogere ondersteunde DDR snelheid een materiele bottleneck hebben op de geheugenkanalen als dat er maar 2 zijn

Er zal verder een logische verhouding tussen Ryzen - Threadripper - Epyc moeten zijn.

Dus denk dat Ryzen mogelijk beetje tegen zal vallen (qua corecount) tov wat ik hoop en inderdaad de "kapotte" chips krijgt met een max van 10, wellicht 12 cores.

Ryzen lijkt me ook nog best ver weg. Q2 als het meezit.

PC Specs

Asus ROG Strix B650E-E | AMD 9800X3D |TR Phantom Spirit 120 SE | G-Skill 32GB DDR5 6000C30 M-die | 4090 FE | LG 3840*1600p 160Hz | Corsair RM1000x Shift

Op core count hebben ze al een serieuze voorsprong op Intel die ze niet zo maar één twee drie zullen inhalen, wat mij betreft mogen ze meer aandacht aan IPC etc. besteden.

Got Leenucks? | Debian Bookworm x86_64 / ARM | OpenWrt: Empower your router | Blogje

In de consumenten desktop (i.c.) heeft AMD geen voorsprong meer en ik zou ook daar wel graag een stap zien in corecount zonder naar Threadripper over te hoeven stappen.Borromini schreef op woensdag 7 november 2018 @ 18:54:

8 cores is toch niet mis voor een consumentenprocessor. De meeste mensen kunnen daar zelfs niks mee (voor veel huis- en tuingebruikers is een quadcore al meer dan ze 99% van de tijd nodig hebben).

Op core count hebben ze al een serieuze voorsprong op Intel die ze niet zo maar één twee drie zullen inhalen, wat mij betreft mogen ze meer aandacht aan IPC etc. besteden.

Ik vind extra cores dan ook niet nutteloos omdat ze regelmatig weinig doen, ik vind ze juist nuttig omdat ze, als ik ze wel nodig heb, ze er zijn en taken dan veel sneller afronden.

Bovendien elk aanbod schept zijn eigen vraag. Alleen dat aanbod moet er wel eerst zijn.

Gelukkig zie je bijv wel games die de extra cores goed gebruiken zoals Battlefield.

BF V heeft inmiddels als aanbevolen requirements voor DXR een hexacore en octacore.

Uiteraard zie ik ook graag clock en ipc improvements maar daar verwacht ik eigenlijk wel dat Ryzen 3 per core minimaal net zoveel werk kan verzetten als intel cores.

Maar goed ben heel benieuwd wat Ryzen wordt, want misschien zijn mijn verwachtingen wel wat te hoog gespannen.

PC Specs

Asus ROG Strix B650E-E | AMD 9800X3D |TR Phantom Spirit 120 SE | G-Skill 32GB DDR5 6000C30 M-die | 4090 FE | LG 3840*1600p 160Hz | Corsair RM1000x Shift

Verwijderd

Wat Mask zegt, AMD's primaire doel is om meer marktaandeel te verkrijgen en daarvoor moet je redelijke prijzen vragen. Zelfs al zou Zen2 in alle opzichten ruimschoots Intel verslaan dan nog zal de prijs niet veel hoger worden dan dat het nu is voor Ryzen2. Als Intel productie-problemen heeft (in verhouding tot de vraag) en hierdoor de prijzen omhoog zijn geschoten, des te beter voor AMD. Je ziet nu toch ook niet de prijzen van Ryzen2 omhoog schieten? Overigens zijn de prijzen van Intel (8400 en 8600k, de 8700k is nog problematisch duur) de laatste weken alweer fors aan het dalen!

Afhankelijk van de taak, ja. Ze gebruiken niet voor niets 4 geheugenkanalen op de eerste generatie TR-platform met 16 kernen. Dat neemt niet weg dat het in veel scenarios wel nuttig is om die extra kernen te hebben.Help!!!! schreef op woensdag 7 november 2018 @ 17:38:

Tja geheugenkanalen is op zich een goed punt.

Maar zou 16 cores icm mogelijk hogere ondersteunde DDR snelheid een materiele bottleneck hebben op de geheugenkanalen als dat er maar 2 zijn

Met 64 kernen en 16 geheugenkanalen (niet genoemd maar voor de hand liggend) voor Epyc is 32 kernen voor TR met 8 geheugenkanelen mogelijk en zou Ryzen eventueel naar 4 geheugenkanalen kunnen gaan maar ik denk dat de kosten van die extra geheugenkanalen (de kosten van het moederbord in ieder geval, geen idee wat het zou kosten voor de CPU) hierbij het struikelblok vormen en niet zozeer wat AMD zou willen. Het probleem zit m.i. eerder in dat ze teveel defecte kernen gaan hebben met dit nieuwe procedé en dat het daarom gemakkelijk is als ze al die delen kunnen verkopen voor Ryzen. Wij kregen al die "kapotte chips" (net als dat wij de slechtste RAM krijgen, iets om over na te denken wanneer je zoveel betaaltEr zal verder een logische verhouding tussen Ryzen - Threadripper - Epyc moeten zijn.

Ik vind 10 kernen voor een 3600(X) en 12 kernen voor een 3700(X) bepaald niet tegenvallen maar het zou natuurlijk geweldig zijn als de yields dusdanig zijn dat respectievelijk 12 en 14 kernen mogelijk zijn.

Daarnaast speelt misschien nog iets anders mee. Als je strategisch handelt...

AMD weet dat de vooruitgang qua node tussen 2019 en 2020 klein gaat zijn (een soort van Ryzen1=>Ryzen2), mogelijk komt er dan wel Zen3 in 2020 (hopelijk) maar die innovatie van de micro-architectuur gaat ook minder snel gaan na de tweede ronde. Speel het nu conservatief en je hebt volgend jaar weer een leuke sprong van 2 kernen voor beide platforms. Wie gaat er klagen over 'slechts' 4 kernen extra van het ene jaar op het andere jaar terwijl Intel ons 9 jaar lang op een quadcore heeft gehouden? Wie gaat niet onder de indruk zijn van 4 kernen (50-67%meer bij AMD). Dat is een smashing dunk!

Met 15% IPC zitten ze op dat punt al ruim voorbij Intel Coffee Lake, met 25% extra performance zou je op een boost van 1,25*4,3 GHz (5,3 of 5,4 GHz) uitkomen, veronderstellende dat dat de maatstaf is van performance (er staat "frequentie bij hetzelfde vermogen" op die powerpointslide, de vraag is welk vermogen als uitgangspunt werd genomen), en die 25% is het minimum, AMD spreekt niet voor niets van "meer dan 25%". Dat is een kwestie van dat ze (AMD en TSMC) nog van alles aan het tweaken en debuggen zijn. TSMC sprak over 35% en dat je met die node gemakkelijk boven de 5,0 GHz. zou moeten kunnen klokken. Een veel interessantere vraag is in welke mate AMD de latency weet te beperken wanneer data van de ene CCX naar de andere moet want op MS en developers die het fatsoenlijk optimaliseren hoeft AMD duidelijk niet te rekenen. Dat heeft o.a. te maken met hoe goed de RAM werkt en laat AMD daar nu volgens Chiphell veel vooruitgang hebben gemaakt voor Zen2.Uiteraard zie ik ook graag clock en ipc improvements maar daar verwacht ik eigenlijk wel dat Ryzen 3 per core minimaal net zoveel werk kan verzetten als intel cores.

Nu zou 8 van zulke kernen genoeg zijn, over 5 jaar, geen idee. Nadat de PS5 uitkomt zal de CPU-load van spellen fors toenemen, dat is zeker. Daarnaast zijn er zat van toepassingen buiten gaming waarvoor meer kernen beter is.Borromini schreef op woensdag 7 november 2018 @ 18:54:

8 cores is toch niet mis voor een consumentenprocessor.

Ik denk dat die extra kernen in ieder geval erg handig is om sneller meer marktaandeel te krijgen. Als de kern gelijk presteert aan die van Intel dan maken extra kernen/PCIe-lanes...het verschil en de extra kernen is hetgeen wat de doorsnee gebruiker die niets over hardware weet opmerkt. Zeker omdat er mogelijk nog twijfels zijn over bepaalde performance-aspecten zoals de lagere FPS bij oudere spellen of bij spellen waarbij er veel data van de ene CCX naar de andere moet. Waar Help ook op lijkt te doelen, dat zo'n CPU niet snel te oud zal worden door een gebrek aan kernen maakt het veel aantrekkeliijker. Een van de elementen van de presentatie van gisteren die heel erg opviel: "Wij willen verdere innovatie waar de wet van Moore ophoudt". Zowel Lisa Su als Mark Papermaster merkten dat op. Vrij vertaald betekent deze uitspraak: "per kern gaan de prestaties niet meer zo snel zoveel vooruit (doordat de node niet meer zo snel zoveel kleiner wordt en de klokfrequentie niet meer zo snel kan stijgen), wij willen snelle vooruitgang behouden door meer kernen te blijven gebruiken".

[ Voor 40% gewijzigd door Verwijderd op 08-11-2018 04:07 ]

Verwijderd

Toen kon dat ook redelijkerwijze worden vermoed aangezien hij eerder gelijk had gekregen maar het voorbehoud was dat plannen kunnen veranderen...

Hiermee weten we meer dan wat AMD heeft losgelaten. Het aantal kernen en de cache kloppen en die 3200 MT/s werd ook al gezien bij die engineering sample. Van Navi is het bekend dat het PCIe 4.0 ondersteunt en Rome ondersteunt ook PCie4. We mogen dus, lijkt mij, aannemen dat voor Ryzen3 en de volgende generatie AM4-moederborden (de chipset daarin) PCIe4 wordt gebruikt. We weten dat Epyc uit 8 dies met 8 kernen bestaat dus als je uitgaat van 1/4de hiervan dan kom je uit op 32 PCIe-lanes. Ofwel 8 extra PCIe-lanes in vergelijking met de huidige moederborden en dit met PCIe4 voor de grafische kaart. Dat betekent dat we de tweede NVMe gaan kunnen gebruiken zonder dat het ten koste gaat van de grafische kaart.Ne le répétez à personne, mais les CPU EPYC de 2e gen d'AMD auront 64 cores, 256 Mo (!) de L3, 8x DDR4-3200 et 128 lignes de PCIe 4.

Het ligt voor de hand dat ze inderdaad 2 CCX'en gebruiken voor Ryzen3, als je 1/8ste van die Epyc neemt dan kom je uit op 16 PCIe lanes wat niet mogelijk is (in de zin dat het een achteruitgang zou zijn en dat een aanzienlijke groep gebruikers 24 al ietwat krap vonden). Tenzij ze een aparte die zouden maken maar zou dat efficiënt zijn? Niet zozeer vanwege de kosten van het maken van die die, als ze dat voor de APU kunnen doen dan is dat toch zeker ook mogelijk voor de desktop-CPU's? Echter, het gebruiken van ongeschikte stukken voor Epyc en Threadripper voor de desktops is efficiënt en daarom verwacht ik dat je 2 CCX'en krijgt. Dus 10 en 12 als de yields niet tegenvallen en er zijn signalen dat ze niet tegenvallen. Veilige voorspelling (jullie mogen het tegen die tijd citeren, als het niet klopt en als het klopt): minimaal 2 kernen erbij t.o.v. nu, maximaal 6 kernen erbij en eventueel 1 model erboven (en een aanzienlijk hogere prijs) voor een model met 16 kernen.

Dus:

3600(X): 8-12 kernen (functie van yields, waarschijnlijk minstens 10 gezien de positieve berichten tot nu toe)

3700(X): 10-14 kernen (functie van yieids, waarschijnlijk minstens 12 gezien de positieve berichten tot nu toe)

32 PCIe-lanes en PCIe 4.0 voor de grafische kaarten

Verder natuurlijk 32 MB cache en 3200 MT/s voor klokfrequentie.

Mogelijk een 3800X met 14-16 kernen voor een aanzienlijk hogere prijs of een 3800X met 14 kernen en een 3900X of zo met 16 kernen of een 3800X met 16 kernen, voor een aanzienlijk hogere prijs omdat de voorraad beperkt is.

De positieve berichten doen me meer richting 14 kernen voor de 3700X leunen maar de vraag is of dat de yields zo erg meevallen en of dat AMD niet wat headroom wil voor de volgende generatie wetende dat je er al 4 kernen bij doet en dat de hoge managers van Intel het Spaans benauwd krijgen.

Ik vroeg me af of dat de uitdrukking met de Spaanse bezetting van Nederland te maken had dus ik zocht het even op. Interessant om te weten. https://historiek.net/spaans-benauwd-herkomst/79141/

De resterende vraag voor mij: als die 3200 MT/s min of meer gegarandeerd is gaat dan overklokken naar 3600 MT/s met een doorsnee die van Hynix ook mogelijk zijn of is dat 1 stap te hoog en kom je op 3400 MT/s uit? Ik rond de frequenties maar even af voor het gemak.

Tot slot nog een software-puzzelstukje, met 6 kernen of meer op 1 die ligt het voor de hand om voor oudere spellen en minder oude slecht geoptimaliseerde spellen en andere programma's alles op 1 die te draaien. Zou AMD met een oplossing komen om dit te doen vanuit het besturingssyteem? Ideaal zou je willen dat je via software kan aangeven dat voor 1 programma bijv. kernen 7 t/m 12 beschikbaar worden gesteld en dat Windows en de rest kernen 1 t/m 6 krijgen? AMD kan gemakkelijk die kernen een identificatiecode geven, maar dan moeten Windows en Linux wel meewerken met de threadscheduling.

Voor mij wordt dit een leuke upgrade: van 4 trage kernen zonder HT (i5-750) naar 10-14 snelle kernen met SMT. Dat is nog beter dan van een Pentium4 naar de i5-750.

Laat maar komen!

6 maar? Waarom dan niet 8? Ik denk dat je die 8 toch wel graag hebt over een paar jaar. Zeker als je met een hoge FPS wil gamen met hoge grafische instellingen (maar niet 4k).Vlizzjeffrey schreef op donderdag 8 november 2018 @ 07:26:

Hoop dat ze met een 6 core op 1 ccx komen, beniewd hoe snel dat zou zijn in games.

[ Voor 110% gewijzigd door Verwijderd op 08-11-2018 09:30 ]

Daar kunnen ze niet al te ver in gaan tho, omdat ze dan met 1e en 2e generatie Threadripper aan het concurreren zijn, die miss wel beter te koelen zijn vanwege het grotere oppervlak. M.a.w. ik denk dat een 3000-series 16-core aan het uiterste eind €1.000,- zal zijn, wat nog steeds vrij fors is, maar niet onrealistisch of onverwacht wanneer je naar de huidige lineup kijkt.Verwijderd schreef op donderdag 8 november 2018 @ 08:01:

Mogelijk een 3800X met 14-16 kernen voor een aanzienlijk hogere prijs of een 3800X met 14 kernen en een 3900X of zo met 16 kernen of een 3800X met 16 kernen, voor een aanzienlijk hogere prijs omdat de voorraad beperkt is.

Hopelijk wordt ie natuurlijk een stuk minder dan dat.

PC: R9 5950X | 32GB | VEGA 64 Liquid Edition

Verwijderd

Nu even niet. Ik houd hier graag maixmale nuance.

Dat is mogelijk ook een bezwaar maar daar ben ik nog niet van overtuigd. Threadripper gaat t/m 32 kernen en ja, de 2920X en 2950X zouden dan in prijs dalen maar hier staat tegenover dat die nu al niet zo heel erg duur zijn (in Nederland is de prijs flink geïnflateerd (retail-probleem), in de USA betaal je er $699 voor bij Newegg) en dat AMD eerder de prijzen gigantisch verlaagde voor Threadripper1 en Ryzen1. AMD heeft daar blijkbaar geen moeite mee zolang het marktaandeel maar flink stijgt en de nieuwe stack op dezelfde prijzen of hoger (Threadripper2, meer kernen en hogere prijzen) uitkomt. win/win: klant blij en AMD blij. Daarnaast mag TR wat duurder zijn omdat het platform meer high/end is (PCIe-lanes, I/O, geheugen-kanalen). Hoewel een 12c-3700X of 12C-3600X qua brute 'reken'kracht de 2950X zou verslaan. We mogen rond augustus 2019 Threadripper3 verwachten en dat gaat een lekkere upgrade zijn voor mensen die voor dat platform kiezen, die wachten wel rustig op TR3 of vinden het niet erg om nu al het platform te kopen en later die TR2 CPU te verkopen en een TR3-CPU te kopen (ze kunnen het betalen en ze hebben het ergens voor nodig). De enige kwestie voor AMD is om dan de productie voor TR2 op tijd te verminderen voordat Ryzen3 uitkomt of ervoor te zorgen dat de voorraad niet al te hoog wordt. Het punt is dat AMD nog meer zou verkopen in 2019 en hier een goede winst mee zou maken. We weten immers dat het pak hem beet $100 (US) kostte om een volle TR1-CPU te maken, de kosten voor een TR2-CPU met 16 kernen zullen lager liggen (verder ontwikkelde node). Met TR en Epyc pakt AMD grote marges, met Ryzen een groot marktaandeel, AMD heeft beide nodig (hoger marktaandeel => beter adoptie van Epyc).Gelunox schreef op donderdag 8 november 2018 @ 09:31:

[...]

Daar kunnen ze niet al te ver in gaan tho, omdat ze dan met 1e en 2e generatie Threadripper aan het concurreren zijn, die miss wel beter te koelen zijn vanwege het grotere oppervlak.

Ik zie zelf meer een probleem bij het bewaren van headroom voor de generatie daarna. Het is een mokerslag richting Intel als er respectievelijk 67% en 50% kernen bij komt voor de 3600(X) en de 3700(X) t.o.v. de 2600(X) en de 3700(X). Niet alleen omwille van hun monolithische ontwerp, ook omwille van hun productstack waarbij de prijs gigantisch sterk toeneemt voor de betere CPU's met veel kernen en we weten dat Intel met hun monolithisch ontwerp niet veel meer kan dan 28 kernen en zelfs dat is al kantje boord.

Zie het recente bericht dat Intel een dual-die CPU met 2*24 kernen wil uitbrengen (zo schattig

Die AMD-medewerker die in mei lekte richting WCCFTech (geen idee waarom maar blijkbaar klopte het, er werd hier nog door iemand gesuggereerd (ik herinner wie maar ik noem geen naam) dat er met opzet valse informatie werd verspreid om een mol uit te roken)) aan dat ze streven naar 16 kernen.

De laatste zin slaat natuurlijk op de yields. "might be closer to 12" als ze niet genoeg goede dies met 8 werkende kernen overhouden nadat ze genoeg dies apart hebben gelegd voor de veel meer lucratieve Epyc en Threadripper. AMD streefde toen naar 16 maar in functie van de yields zou dat omlaag gaan naar het aantal kernen wat praktisch gezien haalbaar is.Before closing out this piece I would be remiss if I did not mention one of the most eye-brow raising rumors that we’ve come across and it’s this. AMD is allegedly going to be raising the bar once again next year by pushing the mainstream core count from 8 cores to a maximum of 12 to 16 cores on the AM4 socket.

The rumor out there is that we’re looking at 16 core Ryzen 7 chips as the new norm in 2019. However, according to private conversations we’ve had with incredibly knowledgeable people in the industry the actual core count figure might be closer to 12 cores.

Tenslotte herinner ik aan Lisa Su die bij een investors-Q&A aangaf dat "hun plannen zeer agressief zijn omdat ze hadden verwacht dat Intel verder zou zijn met de 10 nm. node".

Als iemand de bron kan vinden of heeft bewaard: graag.

Bedenk bij deze uitspraak da Lisa Su een uiterst intelligente vrouw is die ook nog eens een zeer vaardige CEO is, zij kiest haar woorden zorgvuldig, als zij "zeer" gebruikt als bijvoegelijk naamwoord dan staat er iets bijzonders op de agenda.

Ik handhaaf voor nu mijn voorspelling. Minstens 8 kernen voor de 3600X en maximaal 10 kernen voor de 3600X. Twee erbij voor de 3700X. Ik ga uit van respectievelijk 10 en 12 gezien de positieve berichten over TSMC 7 nm. van diverse kanten en ik sluit respectievelijk 12 en 14 niet uit (maar ik verwacht het niet)! Mogelijk 14/16 kernen voor 1/2 modellen boven de 3700(X). Fors duurder voor het laatste, ja, maar wel ruim onder de €1000!! Ik denk aan een premie van €100-150 t.o.v. het model eronder. Je ziet immers sinds ze de prijzen van de 1700X en 1800X hebben verlaag dat de prijs redelijk proportioneel stijgt met het aantal kernen met iets minder waarde per € bij meer kernen boven de *600.

Die €1000 voorspelling voor de high-end komt me bekend voor van de eerste generatie. Ik zei toen ook van tevoren dat het niet meer dan €500-600 zou zijn en eigenlijk geloofde ik in niet meer dan €500 (gebaseerd op Koduri zijn opmerking in mei 2016 dat marktaandeel alles is en gebaseerd op het feit dat AMD nog een lichte achterstand had voor de single-core t.o.v. Intel en flink wat scepsis moest overwinnen) maar ik liet me gek maken door iedereen die dat stelde. AMD is uiterst agressief met de CPU's en Intel heeft jarenlang grof misbruik gemaakt van hun 'monopolie'. AMD wil ook graag agressief zijn met de GPU's maar dat kan niet omdat de marges bij GPU's zo klein zijn en dat geldt ook voor de partners van AMD en Nvidia (ongeveer 3% marge voor die partners volgens GamersNexus). Bovendien gaf AMD aan dat de productie 70% goedkoper is dan bij een monolithisch model, ook dat speelt mee maar het is niet helemaal duidelijk waar die 70% precies op slaat, dat mag AMD wat concreter maken. Het is niet dat dat een bedrijfsgeheim hoeft te zijn want bij Intel kunnen ze dat ook wel uitrekenen.

[ Voor 28% gewijzigd door Verwijderd op 08-11-2018 10:24 ]

Je maakt Ryzen 3000 zo wel heel duur. Qua specs zit je zo ongeveer op de eerste Threadrippers, maar dan zonder de geheugenbandbreedte.

Waarom niet gewoon 8 cores en 16 threads met iets hogere IPC en klokfrequentie, lager verbruik en beter power management? Ook daarmee heeft AMD een prima concurrent voor Intel's huidige desktop line-up en met betere power management kunnen ze ook beter concurreren op laptop gebied. Vergeet niet dat AMD al heeft aangegeven dat 7nm dubbel zoveel moet kosten. Daarnaast 8c16t voor een desktop CPU is natuurlijk ook nogal eens flink aantal, meer cores en threads schalen niet echt bij desktop software.

Dan heb je Threadripper voor bijvoorbeeld 12 tot 32 cores en Epyc tot 64 cores. Heeft Threadripper ook meer functie. Met 16c32t en 32 PCI Express 4.0 lanes is er nog weinig functie voor Threadripper. Alleen heeft zo'n CPU wel een geheugenbandbeedte te kort en kun maar een kwart van de bandbreedte van je PCI Express sloten gebruiken op de huidige moederborden. Ook daarom is zo'n CPU niet echt logisch.

Misschien geen 4 CCX modules per AM4 cpu, maar met slecht 2 kun je ook nog steeds een octocore inelkaar knutselen. We gaan geen volledig functionele CCX'en zien op AM4, dat is te duur.NitroX infinity schreef op zaterdag 6 oktober 2018 @ 17:55:

Ik denk dat als er meer kernen in een CCX komen dan momenteel, dat alles met vier of meer kernen werkend, naar Threadripper en Naples zal gaan en dat we voor AM4 alleen modules met drie (heel misschien vier) of minder werkende kernen zien. Wel dan vier CCX modules per processor voor socket AM4 en acht voor Threadripper en Naples.

Puur vanuit een financiëel oogpunt lijkt me dat het meeste geld op te leveren voor AMD.

[ Voor 4% gewijzigd door NitroX infinity op 08-11-2018 10:38 ]

Graphene; a material that can do everything, except leave the lab. - Asianometry

Verwijderd

De productiekosten voor de volle 16C TR zouden rond de $100 hebben bedragen mid/eind 2017 (rond augustus/september), dan kom je voor de 8c Ryzen uit op minder dan $50. De extra productiekosten hoeven niet zo'n probleem te zijn, ik denk dat dat deel wordt overdreven. Laten we uitgaan van een verdubbeling van de productiekosten. Zeg het maar als jij denkt dat het nog duurder kan worden. Dan kom je uit op $50 extra kosten voor zoveel extra performance. Mogelijk gaat de prijs wat omhoog maar dat lijkt me ook niet zo'n ramp. Mogelijk neemt AMD genoegen met iets minder marge per CPU omdat het markthaandeel stijgt.Verwijderd schreef op donderdag 8 november 2018 @ 10:32:

@Verwijderd

Je maakt Ryzen 3000 zo wel heel duur. Qua specs zit je zo ongeveer op de eerste Threadrippers, maar dan zonder de geheugenbandbreedte.

Waarom niet gewoon 8 cores en 16 threads met iets hogere IPC en klokfrequentie, lager verbruik en beter power management? Ook daarmee heeft AMD een prima concurrent voor Intel's huidige desktop line-up en met betere power management kunnen ze ook beter concurreren op laptop gebied. Vergeet niet dat AMD al heeft aangegeven dat 7nm dubbel zoveel moet kosten. Daarnaast 8c16t voor een desktop CPU is natuurlijk ook nogal eens flink aantal, meer cores en threads schalen niet echt bij desktop software.

Dan heb je Threadripper voor bijvoorbeeld 12 tot 32 cores en Epyc tot 64 cores. Heeft Threadripper ook meer functie. Met 16c32t en 32 PCI Express 4.0 lanes is er nog weinig functie voor Threadripper. Alleen heeft zo'n CPU wel een geheugenbandbeedte te kort en kun maar een kwart van de bandbreedte van je PCI Express sloten gebruiken op de huidige moederborden. Ook daarom is zo'n CPU niet echt logisch.

Ja, ik ben me er bewust van dat €X productiekosten leidt tot een >€X hogere prijs gezien marges bij de distributieketen en retail en belastingen maar dat maakt niet het grote verschil, dan kom je misschien uit op 1,1*1,1*1,21*$50, net iets boven de $70.

Waarom meer kernen?

- Het belangrijkste. Je komt niet aan het vereiste aantal PCIe-lanes, 16 zou te weinig zijn en 1/8ste van de eerder genoemde128 (Canard) is 16. Wat wil je doen? 8 lanes PCIe4 per grafische kaart heeft evenveel bandbreedte als 16 lanes PCIe3 en dan kom je dus lanes tekort om en 2 grafische kaarten te huisvesten en NVMe SSD's via M.2 en eventueel nog wat anders (geluidskaart, capturekaart...).

- Dan kan je dus een aparte die maken maar dat is niet praktisch, wat doe je met alle stukken waar beschadigde kernen in zitten die niet geschikt zijn voor Epyc en Threadripper? Die ga je dan kunnen weggooien, dat lijkt mij weinig efficiënt bij zo'n jonge node waar je ongetwijfeld nog wat yield-problemen gaat hebben.

- Su gaf aan bij die investors-Q&Adat AMD zeer agressieve plannen heeft omdat het verwachtte dat Intel tegen die tijd wel een fatsoenlijke 10 nm. node zou hebben (geparafraseerd). Een kwestie van interpretatie/mening, ik vind hetzelfde aantal kernen en slechts snellere kernen (en het voor de meeste mensen relatief kleine nadeel wanneer data van de ene CCX naar de andere moet) niet zeer agressief, eerder aan de slappe kant.

- Gebruik twee CCX'en en je kan het volgende jaar er ook weer een schepje op doen wanneer er minder laaghangend fruit is voor de micro-architectuur (derde ronde, geen nieuwe node die een verdubbeling van het aantal bits of cache of zo mogelijk maakt) en hoewel de tweaks de TSMC 7 nm. node zullen verbeteren gaat het om relatief kleine verschillen

- Het feit dat zowel Su als Papermaster zo stevig hamerden op: "Moore's law is aan het beëindigen, wij willen de innovatie voortzetten." Dat interpreteer ik als: per kern wordt het niet veel beter (de klokfrequentie kan niet veel meer stijgen, in ieder geval niet bij X86), wij blijven vooruitgang maken door meer kernen te blijven aanbieden. Ik sluit me aan bij Help die stelt dat de software zich aanpast aan de beschikbare hardware. Qua hardware heeft AMD nog een belangrijke troef de consoles: stop daar 1 die met 8 kernen in en 1 die met Navi-graphics en die 8 kernen worden wel gebruikt en je legt Intel nog meer het vuur aan de schenen.

- AMD wil elke generatie er een schep bovenop doen. Een snellere kern is leuk en aardig maar ik denk niet dat AMD hier genoegen mee zou nemen. Een gutfeeling gebaseerd op hoe gretig AMD is m.b.t. het laten toenemen van het marktaandeel.

[ Voor 4% gewijzigd door Verwijderd op 08-11-2018 11:38 ]

Waar haal je dat weg? AMD zal zoiets nooit bekend maken en iemand anders kan alleen maar extreem wilt gokken en daarbij prima honderden procenten er naast zitten.Verwijderd schreef op donderdag 8 november 2018 @ 11:32:

[...]

De productiekosten voor de volle 16C TR zouden rond de $100 hebben bedragen mid/eind 2017 (rond augustus/september), dan kom je voor de 8c Ryzen uit op minder dan $50.

Zelfde als nu, dan heb je al een bandbreedte verdubbeling met PCI Express 4.0. Dus 16 PCI Express 4.0 lanes voor de twee of één PCI Express x16 sloten voor de videokaarten. 4 PCI Express 4.0 lanes voor een M.2 SSD en 4 naar de controller op het mobo voor extra SATA, netwerk, USB, etc.Het belangrijkste. Je komt niet aan het vereiste aantal PCIe-lanes, 16 zou te weinig zijn en 1/8ste van de eerder genoemde128 (Canard) is 16. Wat wil je doen? 8 lanes PCIe4 per grafische kaart heeft evenveel bandbreedte als 16 lanes PCIe3 en dan kom je dus lanes tekort om en 2 grafische kaarten te huisvesten en NVMe SSD's via M.2 en eventueel nog wat anders (geluidskaart, capturekaart...).

[ Voor 47% gewijzigd door Verwijderd op 08-11-2018 11:50 ]

Verwijderd

Een leak die in augustus/september hier uitgebreid besproken. Op zich lijkt het mij ook niet onrealistisch qua productiekosten. Zie de pak hem beet €160 waarvoor de 8400 aanvankelijk verkocht werd. Dat is inclusief een hele gezonde marge voor Intel, R&D-kosten, allerlei andere bedrijfs-operationele kosten (administratie, schoonmaak, beveiliging...), marges bij de distributieketen(s) en retailer en belastingen. En dit op een chip met naast die 6 kernen ook nog geïntegreerde graphics en met een monolithische bouw (lagere kosten bij 2 stukken van 4 CPU's). Ik baseer het echter op die leak die hier in die tijd uitgebreid is besproken, andere mensen hier zullen het zich ook wel herinneren. Voor de duidelijkheid, R&D kosten reken ik niet tot de productiekosten ondanks dat die kosten gemaakt moeten worden om de chips te kunnen maken maar die kosten worden gecoverd door alle segmenten samen en zijn toch al gemaakt voor Epyc, TR, low power apparaten...die kosten zijn niet Ryzen-specifiek.Verwijderd schreef op donderdag 8 november 2018 @ 11:38:

[...]

Waar haal je dat weg? AMD zal zoiets nooit bekend maken en iemand anders kan alleen maar extreem wilt gokken en daarbij prima honderden procenten er naast zitten.

Ach ja, in begin januari (is het CES?) zal AMD hopelijk vertellen hoe het zit m.u.v. de prijs en de exacte boost/klokfrequenties. De vorige twee jaren gebruikten ze dat evenement om meer over Ryzen te vertellen. De hype opbouwen een paar maanden voor de launch...

Daarvoor verwijs ik naar een reactie van Vipeax van 2 dagen geleden in de Intel-draad.Zelfde als nu, dan heb je al een bandbreedte verdubbeling met PCI Express 4.0. Dus 16 PCI Express 4.0 lanes voor de twee of één PCI Express x16 sloten voor de videokaarten. 4 PCI Express 4.0 lanes voor een M.2 SSD en 4 naar de controller op het mobo voor extra SATA, netwerk, USB, etc.

Paprika in "Intel Nieuwsdiscussietopic"

8 lanes voor 2 grafische kaarten is aan de krappe kant voor highend. Daar red je het nu nog mee maar 2 generaties verder...?

Bovendien is het ook wel fijn als je 2 NVMe-SSD's kan gebruiken. Ik denk niet dat 16 PCIe-lanes volstaat maar het is niet onmogelijk. Is het bovendien mogelijk om bijvoorbeeld 6 lanes beschikbaar te stellen per grafische kaart? Moet dat niet 1, 2, 4, 8 of 16 zijn? Ik volg jouw logica dat 16 PCIe4 lanes meer bandbreedte geven dan 24 PCIe3 lanes (dat had ik ook al bedacht) maar je gaat het ook nog moeten opdelen en je wil ook aar wat vooruitgang maken. Het is niet onmogelijk maar ook qua aantal PCIe-lanes ligt het voor mij wat meer voor de hand dat ze een kwart van Epyc nemen. Tenslotte ook omdat voor Ryzen1 en Ryzen 2 de verhoudingen zo waren: TR = 2*Ryzen en Epyc = 2*TR. Grofweg in ieder geval, ik heb het niet voor elk detail gecontroleerd.

[ Voor 54% gewijzigd door Verwijderd op 08-11-2018 11:55 ]

Maar PCI Express 4.0 verdubbeld dus zoals gezegd de bandbreedte, dus je hebt al dubbel zoveel beschikbaar. Waarom zou het verviervoudigd moeten worden voor een "simpele" desktop CPU?Verwijderd schreef op donderdag 8 november 2018 @ 11:43:

[...]

Daarvoor verwijs ik naar een reactie van Vipeax van 2 dagen geleden in de Intel-draad.

Paprika in "Intel Nieuwsdiscussietopic"

8 lanes voor 2 grafische kaarten is aan de krappe kant voor highend. Daar red je het nu nog mee maar 2 generaties verder...?

Bovendien is het ook wel fijn als je 2 NVMe-SSD's kan gebruiken. Ik denk niet dat 16 PCIe-lanes volstaat maar het is niet onmogelijk. Is het bovendien mogelijk om bijvoorbeeld 6 lanes beschikbaar te stellen?

Verwijderd

Zie de gewijzigde reactie. Dat deel van jouw reactie ontbrak toen ik reageerde. Ik zie een probleem in de verdeling van de lanes, ik denk niet dat ze nog op het equivalent van 16 lanes voor de grafische kaart(en) willen blijven steken, dat is naar de toekomst toe aan de krappe kant, zeker als je twee grafische kaarten (topsegment Nvidia!) wil gebruiken en al helemaal als je die 2 grafische kaarten en 2 NVMe's gebruikt. Het zou geen verviervoudiging zijn 64/24) maar inderdaad wel een hele forse toename, doch hoofdzakelijk te wijten aan de verbeterde PCIe en niet aan de chipset/micro-architectuur. Ik ben het overigens zeker met jou eens dat 32 PCIe4-lanes complete overkill is voor een desktop CPU maar is het niet al lang zo dat we een complete overkill hadden? Sinds wanneer hebben we PCIe3? Sinds 2008 toen net de quadcore opkwam en nog duur was (de i5-750 kwam in 2009 uit)? Overkill qua PCIe zijn we gewend, het begint nu pas krap te worden in extreme scenario's (bijv. een 2080 Ti met 2 NVMe SSD's bij X470).Verwijderd schreef op donderdag 8 november 2018 @ 11:54:

[...]

Maar PCI Express 4.0 verdubbeld dus zoals gezegd de bandbreedte, dus je hebt al dubbel zoveel beschikbaar. Waarom zou het verviervoudigd moeten worden voor een "simpele" desktop CPU?

[ Voor 65% gewijzigd door Verwijderd op 08-11-2018 12:03 ]

Dus die 2080 Ti + 2 NVME's is een probleem creëren dat vrijwel niet voorkomt. En als je echt die lanes nodig hebt, dan heb je waarschijnlijk ook wel Threadripper nodig, wat het probleem van te weinig lanes oplost. (We hebben het toch over AM4? Of zit ik weer scheel te lezen?)

Graphene; a material that can do everything, except leave the lab. - Asianometry

Ik kan geen niet professionele of zeer niche applicatie bedenken die ook maar iets heeft aan meer dan 8c/16t. Ben je echt serieus bezig met videobewerking of VM's draaien, dan koop je maar een TR. Krijg je ook zaken zoals quad channel memory en dan heb je dan ook wat aan.

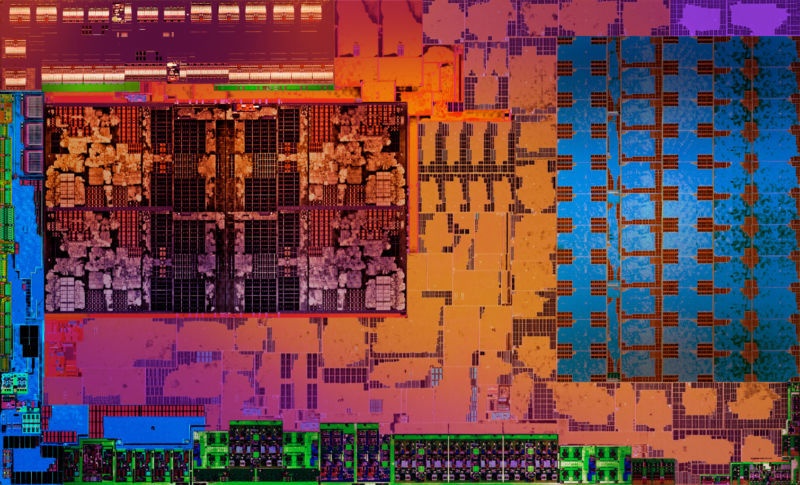

Verder als je kijkt naar de Zen 2 dies en ze vergelijkt met Zen 1 haar 213mm2, dan lijkt een schatting van circa 80mm2 realistisch voor het formaat van een chiplet. Voor Epyc 2 plaatst AMD de chiplets in paren van twee naast elkaar. Ik vermoed dat ze dit doen omdat ze dan net genoeg oppervlakte behalen om de IHS succesvol te solderen. Oh en bedankt voor het plaatje @Paprika. Hoef ik het zelf niet op te zoeken.

Dan is op zich nog best fors voor een 8c chiplet. Een Zen 1 was uit mijn hoofd 44mm2 voor de 8c + cache. Natuurlijk komt er voor Zen 2 natuurlijk nog wat bij, maar bij lange na niet genoeg voor een copy paste van Zen 1 met wat kleine tweaks. Het verschil zal zitten in de 32MB L3 cache, bredere FPU's, maar ik vermoed ook in extra ruimte voor clockspeeds en potentieel ook meer ALU's per core.

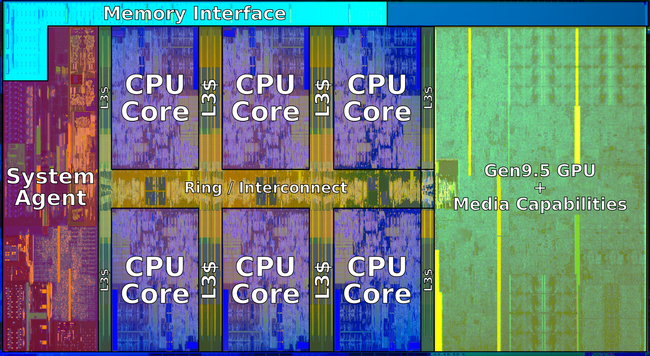

Daarnaast heeft Rome die gigantische I/O die die bedoeld is voor maximaal acht chiplets. Die zie ik AMD hergebruiken voor elke Epyc 2 en TR3 CPU. Voor Ryzen 3000 verwacht ik dat AMD een aparte I/O die gaat introduceren. Eentje die waarschijnlijk vergelijkbaar zal zijn in formaat met een 8c chiplet. Die kunnen ze dan hopelijk naast elkaar plaatsen op een interposer waardoor ze hopelijk nog net de IHS kunnen solderen.

Ik zie dus geen enkele reden waarom AMD met twee 8c chiplets en een grotere I/O chip moet komen dan strikt noodzakelijk voor het marktperspectief van Ryzen. Een dergelijk product zal alleen maar in de TR verkopen inhakken en marges enorm onder druk zetten. Verder is er ook nog een groot praktisch bezwaar te bedenken. Hoe gaan twee 8c chiplets en een I/O die precies passen op de substraat van een AM4 socket chip?

Dit is een Ryzen 1000 en die paste maar net. Overigens lijkt het wel alsof AMD het solderen in twee stappen deed. Dat zou kunnen betekenen dat ze Ryzen 3000 ook kunnen solderen.

edit: Dan PCI-E 4.0. Tja, ik vraag me af of AMD er niet voor gaat kiezen om Ryzen 3000 op PCI-E3.0 te houden. Voor zover ik het begrijp komen de PCI-E lanes allemaal uit de I/O die en zou de chiplet onafhankelijk moeten zijn van PCI-E 3.0 of 4.0. AM4 ondersteunt ook geen PCI-E 4.0 en ik betwijfel of AMD het zomaar erin wil stoppen.

[ Voor 6% gewijzigd door DaniëlWW2 op 08-11-2018 12:48 ]

Never argue with an idiot. He will drag you down to his own level and beat you with experience.

Verwijderd

Hoe meer kernen AMD pusht hoe moeilijker Intel het krijgt met hun monolithische microarchitectuur en ik zie meer dan 8 kernen nog nuttig zijn voor desktop-applicaties, meer dan 16 kernen voor de voorzienbare toekomst niet (maar op de lange termijn waarschijnlijk wel). Stel dat AMD bij 8 kernen blijft, wat dan volgend jaar met een nauwelijks verbeterde node en weinig verbeteringen voor de micro-architectuur (in vergelijking met Zen1=>Zen2)? Gaan mensen kiezen voor AMD als het 6C AMD vs. 6C Intel is en 8C AMD vs. 8C Intel met niet een verpletterend verschil in prestaties in het voordeel van AMD? Waarom gaf Su aan dat hun plannen ZEER AGRESSIEF zijn als ze slechts bij hetzelfde aantal kernen blijven?

Ik weet dat nu voor gaming meer dan 8C nog niet nuttig is maar er is meer dan gaming en ook voor gaming gaan die 8C's behoorlijk standaard worden als AMD en Intel maar genoeg CPU's verkopen met 8C of meer. Hoe hoger het aantal kernen hoe moeilijker Intel het krijgt. Voor de PS5 zou AMD dan 1 CCX met 6-8 kernen en Navi graphics kunnen gebruiken, AMD gaat daar niet slechts 4 kernen voor gebruiken. Het is wachten totdat de developers eindelijk eens van DX11 en DX9 afstappen voor zwaarder draaiende spellen (voor een independent zoals FTL of een 2D spel zoals CUphead/Ori hoef je dat natuurlijk niet te doen) en vanaf dat moment ga je ongelofelijk nuttig die kernen kunnen gebruiken. Alleen al voor collision detection en hitboxes kan je gemakkelijk minstens 1 kern opofferen. Voor realistische physics (niet PhysX alvorens iemand daar weer mee komt) kan je gemakkelijk 2 kernen opofferen, voor NPC's kan je gemakkelijk 2 kernen opofferen, voor AI kan je gemakkelijk 2 kernen opofferen. Zo gauw developers niet meer vastzitten aan een singlethreaded graphics API wordt het mogelijk om dit soort algorithmes uit te werken. Als AMD veel kernen pusht via de desktop en PS5 dan gaat Intel wel mee en het resultaat is dat developers meegaan.

Twee jaar geleden riep iedereen: "waarvoor heb je 8 kernen nodig?". BF5 raadt nu minstens een hexacore aan en dat is zeker niet overdreven op basis van BF1.

Had je het hierboven niet over het verdubbelen van de 16 PCI Express lanes naar 32? Los van overige PCI Express lanes die niet voor de videokaart(en) gebruikt worden.Verwijderd schreef op donderdag 8 november 2018 @ 11:56:

[...]

Het zou geen verviervoudiging zijn 64/24) maar inderdaad wel een hele forse toename, doch hoofdzakelijk te wijten aan de verbeterde PCIe en niet aan de chipset/micro-architectuur.

Er zijn wel toepassingen die iets met een NVMe SSD kunnen met meer bandbreedte en niets hebben aan het aantal core's van Threadripper. Alleen voor gaming of huis-tuin en keuken PC is een SATA-600 SSD prima en voegt een snellere niks toe.NitroX infinity schreef op donderdag 8 november 2018 @ 12:28:

Meh, NVME is niet nodig voor een reguliere consumenten desktop. SATA-600 voldoet nog prima.

Ja AM4.(We hebben het toch over AM4? Of zit ik weer scheel te lezen?)

Omdat de volgende generatie videokaarten ook gebruik gaat maken van PCI Express 4.0, zelfde zal ook ongetwijfeld gelden voor NVMe SSD's, die zullen ook overstappen naar PCI Express 4.0. Zou dan niet echt logisch zijn dat AMD dan nog met PCI Express 3.0 zit.DaniëlWW2 schreef op donderdag 8 november 2018 @ 12:45:

edit: Dan PCI-E 4.0. Tja, ik vraag me af of AMD er niet voor gaat kiezen om Ryzen 3000 op PCI-E3.0 te houden. Voor zover ik het begrijp komen de PCI-E lanes allemaal uit de I/O die en zou de chiplet onafhankelijk moeten zijn van PCI-E 3.0 of 4.0. AM4 ondersteunt ook geen PCI-E 4.0 en ik betwijfel of AMD het zomaar erin wil stoppen.

Het aantal core's bepaald niet hoe agressief je de nieuwe generatie in de markt zet, dat doet de prijs. Als ze met een Ryzen 3000 8c16t in de buurt komen van een i9 9900K en geeft hem dezelfde prijs als een Ryzen 7 2700X dan ben je al heel agressief bezig. Op dit moment is zo'n prijs namelijk minder dan de helft van een i9 9900K.Verwijderd schreef op donderdag 8 november 2018 @ 11:32:

Su gaf aan bij die investors-Q&Adat AMD zeer agressieve plannen heeft omdat het verwachtte dat Intel tegen die tijd wel een fatsoenlijke 10 nm. node zou hebben (geparafraseerd). Een kwestie van interpretatie/mening, ik vind hetzelfde aantal kernen en slechts snellere kernen (en het voor de meeste mensen relatief kleine nadeel wanneer data van de ene CCX naar de andere moet) niet zeer agressief, eerder aan de slappe kant.

Je hebt dan een veel betere performance/watt, prestaties die bijna vergelijkbaar zijn en PCI Express 4.0. Waarbij je dus 16 PCI Express 4.0 lanes hebt voor twee videokaarten en 4 PCI Express 4.0 lanes voor een M.2 SSD die dus max 8000MB/s kan lezen/schrijven.

Op dit moment moet je gewoon een tijd lang met zo'n CPU meekunnen. Er is een lange tijd geweest tussen Sandy Bridge en Kaby Lake waar we amper meer prestaties kregen in het desktop segment. Hierdoor was in de tijd van Sandy Bridge een CPU als een i5 2500K een hele snelle game CPU, maar in de tijd van Kaby Lake was een i5 7600K een CPU die moeite had met moderne games.

Dat is niet iets waar we nu last van hebben. We gaan nu met grote stappen vooruit. De huidige desktop CPU's zijn dan nu snel genoeg voor een game PC en dat zal de komende jaren ook nog wel even zo blijven.

Ja, een Ryzen 3000 met PCI Express 4.0 zal op de huidige AM4 moederborden gewoon PCI Express 3.0 hebben als max.Fleximex schreef op donderdag 8 november 2018 @ 13:31:

Zou een AM4 300 of 400 serie chipset met een Ryzen 3000 CPU (die dan PCI-e 4.0 heeft) gewoon werken met PCI-E 4.0 omdat de PCI-E 3.0 sloten in feite hetzelfde zijn? Of zit er nog iets op het moederbord dat de PCI-E versie specificeert?

Verwijderd

Ik keek naar het totale aantal PCIe-lanes, tenzij ik mij vergis is dat 24 voor Ryzen1/2.Verwijderd schreef op donderdag 8 november 2018 @ 13:40:

[...]

Had je het hierboven niet over het verdubbelen van de 16 PCI Express lanes naar 32? Los van overige PCI Express lanes die niet voor de videokaart(en) gebruikt worden.

Ja, maar die prijs van de 9900k blijft in dat geval niet zo extreem hoog. Hoeveel denk jij dat het Intel kost om die 8C-CPU te maken als een 6C-CPU te koop was voor ongeveer €160 in een Nederlandse winkel (vaste prijs, geen aanbieding). Daar zit een bijzonder hoge marge op, Intel kan de prijs fors verlagen. Ik zie het gewoon niet voor me dat AMD nu al blijft bij hetzelfde aantal kernen, ik denk dat AMD het nog verder wil pushen omdat AMD zo agressief mogelijk het vuur aan de schenen van Intel wil leggen. Stel dat ze de prijs met €25 verhogen (die ruimte is er gezien de prijzen van Intel) en dan zoveel extra kernen kunnen bieden, ze nemen €25 'verlies' per sample maar met een sterk groeiend marktaandeel, dat trekt mensen over de streep. Dat hoeft niet ineens naar 16C te gaan, het kan starten met 8C voor de 2600 en 10C voor de 2700.Het aantal core's bepaald niet hoe agressief je de nieuwe generatie in de markt zet, dat doet de prijs. Als ze met een Ryzen 3000 8c16t in de buurt komen van een i9 9900K en geeft hem dezelfde prijs als een Ryzen 7 2700X dan ben je al heel agressief bezig. Op dit moment is zo'n prijs namelijk minder dan de helft van een i9 9900K.

Laten we het even omdraaien. Stel dat ze inderdaad 1 CCX gebruiken. Gaan ze dan genoeg goede dies met 8 werkende kernen overhouden voor Ryzen nadat Epyc en TR aan de beurt zijn geweest? En wat als het marktaandeel van Epyc en TR flink groeit? Dat zou mogelijk een risico kunnen zijn afhankelijk van de yields en de marktontwikkelingen.

[ Voor 68% gewijzigd door Verwijderd op 08-11-2018 14:20 ]

Ja maar je had het steeds over van 16 naar 32.Verwijderd schreef op donderdag 8 november 2018 @ 13:41:

[...]

Ik keek naar het totale aantal PCIe-lanes, tenzij ik mij vergis is dat 24 voor Ryzen1/2.

Je kunt chips waarbij één of meerdere core's defecten hebben natuurlijk prima als 6 core verkopen. Ik zou het eerder vreemd vinden als 12 of 14 core model uit brengen waarbij je maar één volledig ingeschakelde die hebt. Dan ga je dus heel veel perfect werkende chips als zijnde defect verkopen en verdien je dus minder. Het topmodel uitbrengen die niet volledig is ingeschakeld lijkt mij echt het laatste wat je als fabrikant moet doen.Laten we het even omdraaien. Stel dat ze inderdaad 1 CCX gebruiken. Gaan ze dan genoeg goede dies met 8 werkende kernen overhouden voor Ryzen nadat Epyc en TR aan de beurt zijn geweest? En wat als het marktaandeel van Epyc en TR flink groeit? Dat zou mogelijk een risico kunnen zijn afhankelijk van de yields en de marktontwikkelingen.

Ik zit meer op de lijn van backwards comptabiliteit behouden en wat kosten van de I/O chip voor Ryzen drukken. Maar PCI-E 4.0 mag van mij gewoon hoor. Ik ga er alleen niet vanuit.Verwijderd schreef op donderdag 8 november 2018 @ 13:40:

Omdat de volgende generatie videokaarten ook gebruik gaat maken van PCI Express 4.0, zelfde zal ook ongetwijfeld gelden voor NVMe SSD's, die zullen ook overstappen naar PCI Express 4.0. Zou dan niet echt logisch zijn dat AMD dan nog met PCI Express 3.0 zit.

Never argue with an idiot. He will drag you down to his own level and beat you with experience.

Verwijderd

Voor zo ver ik 16 noemde ging het enkel over de grafische kaarten, voor zo ver ik 32 noemde enkel over wat je bij Ryzen3 zou krijgen als Ryzen = Epyc/4 (soort van).Verwijderd schreef op donderdag 8 november 2018 @ 14:29:

[...]

Ja maar je had het steeds over van 16 naar 32.

Je gaat er genoeg over moeten houden die 8 goede kernen bevatten om als 3700X te verkopen. Die 6 zal nog wel lukken maar 8 bij deze nieuwe node met kleinere productie-capaciteit nadat alle goede samples die nodig zijn voor Epyc en TR apart zijn gelegd en dit wanneer het marktaandeel van Epyc en TR sterk groeit (zeker voor epyc mogen we een hele sterke groei verwachten)...Je kunt chips waarbij één of meerdere core's defecten hebben natuurlijk prima als 6 core verkopen.

[ Voor 11% gewijzigd door Verwijderd op 08-11-2018 14:55 ]

Ik denk dat je mogelijk niet eens moet kijken naar dat 1/8ste van Epyc. Ben vrij druk geweest de laatste dagen dus nog niet alles kunnen zien, maar het lijkt mij logisch dat de PCIE logica niet in de 7nm dies zit maar in de 14nm i/o die en ze dus makkelijk bij 24 kunnen blijven (of misschien naar 32 lanes kunnen gaan) voor RyzenVerwijderd schreef op donderdag 8 november 2018 @ 14:52:

Geen PCIe3 en 1/8ste van die Epyc die (en dus slechts 16 PCIe-lanes wat veel te weinig zou zijn met PCIe3) gaat het natuurlijk niet worden. Dan zal je een aparte die voor Ryzen3 moeten hebben en dan kan van alles gebeuren.

Just had confirmation (Scott Aylor of AMD) on high frequency low core count while maintaning the rest of EPYC ROME’s strengtth (octa channel mem, 128 PCIe-4 lanes, etc…)

I had a drink with Scott last evening along with Ian Cutress, Paul Alcorn, and Charlie Demerjian.

There are going to be things coming out between now and Rome. Sit tight.

The Infinity Fabric Link between the GPUs provides a unified memory access across the GPUs with a latency of 60-70ns.

Verwijderd

Dat is inderdaad mogelijk, ze zouden twee dies kunnen gebruiken voor dat middelste chiplet maar het moet dan ook lekker aansluiten op de omringende dies, ik weet niet hoe gemakkelijk dat is. Anyway, nog maar een keer dat citaat van WCCFTech waarin werd gesproken over 12-16 kernen, dus twee CCX'en van 8. Ik weet dat WCCFTech niet een goede reputatie heeft maar op het vlak van Ryzen-leaks heb ik nog geen verkeerde informatie bij hen gezien. Ik denk dat jullie onderschatten hoe agressief AMD is met kernen en prijzen. Keer op keer reageren mensen weer verbaasd maar waarom?Dennism schreef op donderdag 8 november 2018 @ 20:37:

[...]

Ik denk dat je mogelijk niet eens moet kijken naar dat 1/8ste van Epyc. Ben vrij druk geweest de laatste dagen dus nog niet alles kunnen zien, maar het lijkt mij logisch dat de PCIE logica niet in de 7nm dies zit maar in de 14nm i/o die en ze dus makkelijk bij 24 kunnen blijven (of misschien naar 32 lanes kunnen gaan) voor Ryzen

"Minstens $1000!! Je bent gek als je denkt dat het minder dan $600 wordt". Het werd €350. De prijsdaling van Ryzen 1 (inmiddels €189 voor de 1700X en €10 minder voor de 1700 bij Azerty!), de prijsdaling van Threadripper waarbij je voor $600 de CPU kon kopen die $1000 kostte. Keer op keer. No way dat AMD genoegen neemt met hetzelfde aantal kernen en hetzelfde PCIe-lanes terwijl die 24 PCIe3 al als te weinig werd ervaren en de kleinere node het prima mogelijk maakt om een stap omhoog te doen.

Waarom krijgt Navi PCIe 4.0 support terwijl we voor 100% zeker weten dat de Navi die in 2019 uitkomt meer dan genoeg heeft aan 16 lanes PCIe3 en waarschijnlijk ook meer dan genoeg heeft aan 8 lanes PCIe3? Om voorbereid te zijn op de toekomst? Misschien. Of om voorbereid te zijn op de volgende generatie van het AM4-platform. Zoals Mask aangaf, die PCIe-lanes zijn wel vaker veranderd bij backwards-compatibiliteit. Backwardscompatibility betekent niet dat je parity hoeft te hebben, de volgende generatie mag best beter zijn zolang je de CPU maar in een X370/X470...kan stoppen en je een oudere Ryzen-CPU in de socket van de X570/B550 kan stoppen.

We zullen het waarschijnlijk over twee maanden wel gaan zien.

Daar kan je over discussiëren. Je kan ook gemakkelijk stellen dat iedereen die klaagt over de snelheid van een SATA-SSD zich aanstelt want in vergelijking met de harde schijf...NitroX infinity schreef op donderdag 8 november 2018 @ 12:28:

Meh, NVME is niet nodig voor een reguliere consumenten desktop. SATA-600 voldoet nog prima.

Uiteindelijk willen mensen altijd beter en er zijn genoeg use-case-scenario's waarbij je het verschil merkt, bijvoorbeeld bij het installeren van software, extraction en compression van grote bestanden/folders en video-rendering. Waarom niet deze groepen gebruikers tevreden stellen als het zo weinig kost? Ik weet niet of dat jij het hebt gemerkt, een 500 GB NVMe-SSD (Samsung/Crucial) kost nu minder kost dan een 500 GB SATA-SSD 1 jaar geleden. De prijs is nog fors hoger maar het prijspunt is zeker aanvaardbaar aan het worden.

Er zit nogal een gat tussen een paar extra PCIe-lanes (4 bij snelheid 3.0) willen en de stap naar het TR platform. Een groot financieel gat. Het TR-platform voor de lagere segmenten (8 kernen, 12 kernen) heb ik zelf sowieso nooit interessant gevonden: geen waarde per bestede €.

[ Voor 61% gewijzigd door Verwijderd op 08-11-2018 23:38 ]

Dat is nu net de fout die AMD steeds opnieuw maakt (4870, Polaris, Ryzen). Hebben ze een keer een doorbraak dan proberen ze de concurrent een hak te zetten door een veel betere prijs/prestatie in de markt te zetten, ten kostte van de marge van AMD zelf en mogelijk voor de markt als geheel. Laten we hopen dat AMD blijft werken aan marge verbetering zodat het een gezond bedrijf wordt in plaats van dat ze nog meer cores rond kostprijs gaan verkopen.

Materiaal kosten van cpu's zijn altijd in de 10tjes geschat overigens. Maar kosten allocatie is een complex concept. Als een fab 5 miljard kost moet die ook terug verdiend worden. Voor Intel staat en valt alles bij volume. Voor AMD minder, die hebben geen eigen fabs (meer). Daardoor zitten er direct heel veel kosten verwerkt in de inkoop prijzen (die wij alsnog niet te zien krijgen). Ook zal AMD niet direct profiteren van meer volume. Het zal juist duurder kunnen worden bij beperkte capaciteit. Je ziet overigens dat TSMC meer marge en winst maakt dan AMD.

Wat mij betreft is AMD goed op weg om voet aan de grond te krijgen in cpu land en ik hoop dat ze vooral niet te gek gaan doen nu...

Hostdeko webhosting: Sneller dan de concurrentie, CO2 neutraal en klantgericht.

Verwijderd

Ik ben het met jou eens dat AMD meer winst moet maken, onder de voorwaarde dat die winst wordt geïnvesteerd in R&D, software-support etc. , maar maak de CPU's maar een paar tientjes duurder en dat je al die extra waarde krijgt. Een hoger marktaandeel bij de enthusiast desktop-gebruiker - in 2017 hun primaire speerpunt - leidt tot een betere branding en dus ook tot meer vertrouwen in de zakelijke markt waar je het grote geld verdient. Ik denk niet dat het genoeg is als AMD parity heeft met Intel wat betreft single core en voor iets minder geld (€50-100) een CPU met evenveel kernen verkoop, AMD moet meer waarde bieden en iets goedkoper zijn.

Nu ga jij wellicht opmerken dat AMD dit in de GPU-markt veel heeft gedaan etc. - als ik deze opmerking niet zou plaatsen

Ik denk dat het winnen van vertrouwen, branding en marktaandeel in combinatie met het jaarlijks uitbreiden van het R&D-budget (wat al is gebeurd en zal blijven gebeuren), de beste strategie is. op die manier kan je steeds betere producten maken die je ook steeds gemakkelijker kan verkopen. AMD was de laatste twee jaar niet genereus, ze hadden realtief (zoals dat een rijtjeshuis spotgoedkoop is in vergelijking met een villa in dit landje) lage prijzen omdat het past in hun strategie om martaandeel en branding op te bouwen. Klanten worden over de streep getrokken door de lagere prijzen en merken dan dat het product goed is => betere branding.

AMD heeft al een beetje het achterste van haar tong laten zien voor wie goed oplet. Ze verhoogden voor Threadripper niet de prijzen maar breidden de stack uit met nog betere producten met nog veel hogere winstmarges in het topsegment. Idem voor Epyc. Ik vermoed dat AMD's strategie is om hetzelfde voor Ryzen te doen: productstack uitbreiden met een redelijke prijsverhoging (min of meer proportioneel met het aantal kernen, eventueel een beetje scheeft zoals 33% meer kernen voor 50% meer geld) en een aanzienlijke performance-verbetering maar ook hogere winstmarges voor de hogere segmenten. Laat 2 CCX'en daar nu een mooie oplossing voor zijn en daarnaast nog de ruimte geven om de komende jaren verder te groeien.

https://semiaccurate.com/...rome-is-indeed-a-monster/Rome is exactly what we said it was in July, a monster with nine die, eight 8C CCXs on 7nm, and one IOX built on 14nm. While our initial speculation on interconnects was incorrect, we recently got more details and added a few bits that are still not public. If you look at the layout, it is clear AMD did the right things for the right reasons.

-Verder gaat het om 70-75mm2 dies. Net iets kleiner dan ik inschatte dus.

-Kennelijk is er geen interposer nodig en zit alles direct op de substraat.

[ Voor 11% gewijzigd door DaniëlWW2 op 09-11-2018 19:37 ]

Never argue with an idiot. He will drag you down to his own level and beat you with experience.

Verwijderd

Dat is belangrijk omwille van die per kern licenties voor bepaalde software. Een vraagje voor @Paprika aangezien hij wat meer over software weet, nu Zen2 dubbel zoveel bits beschikbaar heeft voor instructies (in ieder geval floating point en load/store), kan AMD dan twee 128-bit instructies in 1 zo'n 256-bit instructie plakken? Een soort van Rapid Packed Math? Zo ja, hoe werkt dat dan? Regelt de microcode dat volledig? Speelt de compiler een rol?

Grappig dat Charlie nu even zijn gram haalt m.b.t. al die mensen die het niet geloofden maar volgens mij wisten wij ruim voor die tijd al dat Epyc uit 64 kernen zou bestaan en vermoedelijk 9 chiplets zou hebben. Blijkbaar volgt hij AdoredTV niet en Canard niet.

Grappig genoeg gaven veel mensen die live keken naar de presentatie van AMD wel een shoutout richting AdoredTV.

Over wat AMD verkeerd doet met de marketing.

Jullie kennen deze jongen, minstens twee videos van hem (speculatie over Navi en iets wat ik me niet herinner) werden hier gepost door iemand anders.

Samenvatting. Een neef van Sigmund Freud die betrokken was bij proganda tijdens WOII besloot om deze vaardigheden in te zetten voor het bedrijfsleven. Hij experimenteerde bijvoorbeeld door high-society vrouwen op video-beelden te laten roken om meer vrouwen aan het roken te krijgen.

Fraai individu.

Bedrijven zoals Apple en Nvidia zijn er een meester in om bij mensen op het onbewuste niveau gevoelens op te roepen die zij associëren met het merk doordat die gevoelens worden opgeroepen wanneer het merk in beeld komt. Dat kan via reclame zijn maar ook via die presentaties, de verkoop op de eerste dag waarbij mensen 12 uur kamperen voordat de winkeldeuren openen. Dit verklaart ook het fenomeen fanboys.

[ Voor 37% gewijzigd door Verwijderd op 09-11-2018 20:07 ]

We krijgen twee ontwerpen. Zie quote van een artikel van hardware.info:enchion schreef op dinsdag 6 november 2018 @ 22:54:

[...]

Maw voor Ryzen hebben ze WEL de memorycontroller en PCIE en andere IO op 7nm gemaakt

En dat vervolgens niet op de Epyc Rome CPU gebruikt.

https://nl.hardware.info/...het-met-consumenten-chipsWaar de eerste generatie Epyc server-processors inwendig waren gebaseerd op dezelfde chips als de AMD Ryzen processors voor desktops (zij het vier chips in plaats van één) en dit een lancering in dezelfde periode mogelijk maakte, is dit hergebruik van exact dezelfde chips bij de nieuwe generatie niet meer mogelijk. Sowieso is de getoonde I/O-chip met 8 DDR4-kanelen en 8 Infinity Fabric lanes puur en alleen geschikt voor de Epyc-chips. Mocht AMD op basis van dezelfde CPU-chiplets consumenten-CPU’s op de markt willen brengen, dan moet men dus sowieso een kleinere, minder uitgebreide I/O-chip met dual-channel geheugencontroller, een beperkt aantal PCIe-lanes en slechts één of twee Infinity Fabric verbindingen ontwikkelen. Het is prima mogelijk dat de derde generatie Ryzen chips gaan bestaan uit zo’n kleinere losse I/O-chip gecombineerd met één of twee CPU-chiplets, maar om de uiteindelijke kosten voor hoog volume producten te beperken ligt een monolitische chip met alles in één meer voor de hand. Hoe het ook zij, er moeten dus méér chips ontworpen worden dan voorheen en gezien de beperkte mankracht van AMD mag je verwachten dat eerst de productie en validatie van de chips voor de Epyc “Rome” processors goed op stoom moet zijn, voordat men met andere uitvoeringen in de weer kan.

How do you save a random generator ?

Verwijderd

Dat ze een aparte die moeten gebruiken voor de I/O+IF was wel duidelijk, dat zegt niets over de die die ze gebruiken voor de kernen. Ik ga er in ieder geval van uit dat WCCFTech hun leak klopt. Ze hebben tot nu toe geen verkeerde leaks gehad over Zen en ze hadden er al een paar, blijkbaar hebben ze dus een bron in die industrie. Let erop dat ze het zelf ook nadrukkelijk aangeven dat dit van iemand komt die veel informatie heeft binnen deze industrie en dat het geen wilde speculatie is. Het "tot 16 maar waarschijnlijk eerder 12" verhaal duidt op 2*8 waarbij X kernen beschadigd of uitgeschakeld zijn. Echter zouden de yields goed moeten zijn volgens Semiaccurate (chips ter grootte van telefoon-chips, daar zit wat in aangezien telefoons met zulke chips al een tijdje werden verkocht) en dan zou het misschien meer te maken hebben met een technische beperking (twee geheugen-kanalen) en nog wat gemakkelijk winst voor de volgende ronde (Ryzen4) laten liggen?

Before closing out this piece I would be remiss if I did not mention one of the most eye-brow raising rumors that we’ve come across and it’s this. AMD is allegedly going to be raising the bar once again next year by pushing the mainstream core count from 8 cores to a maximum of 12 to 16 cores on the AM4 socket.

The rumor out there is that we’re looking at 16 core Ryzen 7 chips as the new norm in 2019. However, according to private conversations we’ve had with incredibly knowledgeable people in the industry the actual core count figure might be closer to 12 cores.

Ik heb steeds meer moeite om Tomshardware serieus te nemen (al zijn hun PSU-reviews nuttig). Na eerder dat "je moet veel geld besteden aan die Turing-kaarten en leven voor nu" verhaal waar zo'n beetje iedereen in dat wereldje de spot mee dreef zie ik nu een merkwaardige beste CPU's keuze.

https://www.tomshardware.com/reviews/best-cpus,3986.html

Best value: 8400

Ik kijk nu even naar hun eigen statistiekjes: https://www.tomshardware.com/reviews/cpu-hierarchy,4312.html

AMD Ryzen 5 2600X:

Gaming performance: 98.2

Applications: 57.9

Intel Core i5-8400

Gaming performance: 95.6

Applications: 45.8

Aanzienlijk beter voor multithread (d'uh) en ook beter voor gaming volgens henzelf. Nu komt de score iets lager uit bij bijvoorbeeld een all core overklok van 4,2 GHz. dan bij die PB en XFR waarbij die ene kern kortstondig 4,35 GHz. of zo haalt maar als je de score van de 2600 erbij neemt dan zie je dat ook met die lagere score de 2600 voor gaming meer presteert dan de 8400. Dat Intel het overklokken uitschakelt wil niet zeggen dat je moet negeren dat die 2600 overklokt kan worden. Silicon lottery en zo maar die 4,2 GHz. haal je wel, ook als je pech hebt. Dat die CPU momenteel in de USA $20 duurder is dan de MSRP en in Europa nog veel duurder wordt ook genegeerd, dit terwijl dit 'artikel' begin november is gepubliceerd.

Als ik paranoïde zou zijn dan zou ik vermoeden dat Tomshardware die 8400 kiest om Intel te pacifyen: twee van AMD en twee van Intel.

[ Voor 14% gewijzigd door Verwijderd op 09-11-2018 22:47 ]

The new Ultimate Answer to the Ultimate Question of Life, The Universe, and Everything: Debt: The First 5,000 Years

Zo houd je ook nog 16 cores exclusief voor Threadripper 3. En dan heb je bij de Zen 3 launch met Ryzen 4 nog mooi die stap van 12 naar 16 cores. I.p.v. alleen iets hogere frequenties en een IPC van enkele procenten extra.

Alleen als Intel met een 12 of (10?) core part zal komen zie ik AMD een 16 core Ryzen 3 uitbrengen om zo op alle fronten beter te zijn dan Intel's high-end bij de mainstream processoren.

Quantum computing, Ray/Path-Tracing, Inferred AI, Realistic Physical Damage, AI Crowd Dynamics, Asynchronous Code Rendering. (laatste 2 zelf beredeneerd, is maar om wat denkwijzen te opperen.)foppe-jan schreef op zaterdag 10 november 2018 @ 09:12:

in 1 keer naar 16 op de desktop zal op termijn waarschijnlijk betekenen dat de markt een stuk kleiner wordt, want upgradereden valt (groten)deels weg zodra iedereen 4.5GHz+ CPUs met zoveel cores heeft. Wel beter voor het milieu, I guess.

Vooral de laatste zou voor developers een godsgeschenk zijn.

Nu moeten developers allerlei synchronisatie logica inbouwen in de code om de resultaten van 1 core te blenden met de resultaten van de andere core. (wat als je maar 1 core had niet nodig had)

Met 1000 cores hoeft je software opzich niks meer te schedulen je kan elke instructie gewoon meteen uitvoeren op een vrije core, als er dan toch door een core gewacht moet worden op een resultaat van een andere core dan is die wachttijd zo goed als irrelevant aangezien er bijna geen instructies zijn die verder op in de wachtrij staan. (hangt natuurlijk wel af van intercore latenties, maar daar zal AMD, Intel, Nvidia, MS en ook Linux nogal wat wijzigingen in de processorscheduling gaan doen om dat probleem weg te halen voor developers, is opzich niet veel anders dan bij defragmenteren de meest gebruikte software op het snelle gedeelte van de disk zetten)

Maw des te meer cores er per jaar op de markt zijn des te luier/gemakzuchtiger/gemakkelijker er gecode gaat worden en dus des te belangrijker upgraden wordt.

Anyway verder gaan vooral Physics en AI gaan de main features worden die upgraden gaan afdwingen.

btw nu ik de vergelijking met defragmenteren heb gemaakt, zouden we over een flink aantal jaar disks hebben waar de sectoren bestaan uit PU-cores

Maw dat je een disk kan kopen die 100MC groot is ?

Hoe lang duurt het nog voordat een CPU kleiner is dan 1 bit op een oude harddisk ?

How do you save a random generator ?

Maar idd, voor professionele gebruikers scheelt het een boel.

The new Ultimate Answer to the Ultimate Question of Life, The Universe, and Everything: Debt: The First 5,000 Years

Verwijderd

Omwille van het milieu zou ik inderdaad heel erg graag zien dat het wel zou gebeuren.foppe-jan schreef op zaterdag 10 november 2018 @ 09:12:

in 1 keer naar 16 op de desktop zal op termijn waarschijnlijk betekenen dat de markt een stuk kleiner wordt, want upgradereden valt (groten)deels weg zodra iedereen 4.5GHz+ CPUs met zoveel cores heeft. Wel beter voor het milieu, I guess.

Zou het kunnen dat deze redenatie - dat AMD op de rem trapt - (mede) opkomt doordat Intel jarenlang zo weinig mogelijk vooruitgang maakte: net genoeg om de upgrade voor veel mensen te rechtvaardigen (wat ik al gekkenwerk vond bij een 2600k of beter!) maar niets meer dan dat. Su en Papermaster gaven tijdens de investors-presentattie zeer duidelijk aan dat ze erg ambitieus zijn en dat ze zo snel mogelijk zoveel mogelijk de CPU's willen verbeteren. Dit in combinatie met dat meerdere mensen die over zeer veel kennis beschikken (dan denk ik aan insiders, bijvoorbeeld mensen die AMD, GF, TSMC of een moederbord-bedrijf werken) richting WCCFTech aangaven dat je waarschijnlijk tot 12 kernen zou zien en dat Su eerder zeer duidelijk aangaf dat Zen2 "zeer agressief" waren om te concurreren met een GOEDE Intel 10 nm. (niet wat ze nu hebben en aanzienlijk beter dan wat nu hun streven is). Evenveel kernen rijm ik niet met "zeer agressief", een voorzichtig en uiterst intelligent en verbaal zeer vaardig iemand als haar zie ik niet zo snel zulke woorden gebruiken.

Met de kanttekening dat het een investors-Q&A was maar AMD is behoorlijk transparant en eerlijk m.b.t. Zen, in tegenstelling tot de RTG-tak die weer negatief in het nieuws kwam, deze keer met twijfelachtige benchmarks.

Tenslotte benadrukt AMD ook al 2 jaar dat AMD een sterk signaal wil geven richting de partners dat ze hard blijven werken om zo snel mogelijk zoveel mogelijk ontwikkeling te krijgen in de CPU. AMD heeft er baat bij om snel vooruitgang te maken omdat dit richting OEM's en zelfbouwers een duidelijk signaal is dat je rustig kan investeren in het AMD-platform. AMD kan niet zoals Intel achterover leunen en een minimale vooruitgang maken.

Niet dat het gering is wat ze hebben gewijzigd aan de architectuur

Push naar 10/12 kernen en je zal zien dat meer spellen 8 kernen efficiënt gebruiken en hopelijk gaan developers dan toch eens aandrang voelen om Vulkan (of DX12 als ze het niet kunnen laten

Niemand die goed bij zijn hoofd is en zelf een PC bouwt zou nog voor Intel kiezen in 2019/2020 vanaf dat dat Zen2 uitkomt als de 3600(X) voor pak hem beet €200-250 (zonder enige twijfel een gemakkelijk haalbare prijs, dan mogen de productiekosten met bijna een factor 3 stijgen) 10 kernen biet en de 3700(X) voor pak hem beet €350 12 kernen biedt. OEM's zouden ook flink de druk voelen om deze CPU's op te nemen in veel meer van hun systemen. Bij evenveel kernen en ongeveer dezelfde single-core performance (geef en neem 10%) blijf je toch die twijfel houden bij de mensen die je nog niet over de streep hebt getrokken. "Laat ik maar voor Intel kiezen, de software is hier meer aan angepast/ die naam ken ik tenminste)." Bovendien weet AMD verdomd goed dat Intel niet kan concurreren boven de 8 kernen, die 8 kernen gaan maar nipt (temperaturen 9900k met een maximale klokfrequentie (bij conventionele koeling) van 5,0 GHz. bij de meeste samples, even hoog of lager dan bij de 8700k. Intel heeft geen troef meer in de desktopmarkt als AMD het boven de 8 kernen pusht.