Verwijderd schreef op dinsdag 12 september 2017 @ 18:24:

De grote vraag, waarom heeft AMD er niet meer ROP's op gestopt, als dat inderdaad het probleem is. Ik kan me niet voorstellen dat ze dat dan bij AMD niet al snel in de gaten hadden en dat er dan ook een technische of financiële beperking is om dat te doen.

Ik denk dat ze het voor de release van Fiji al wisten...

Maar hoe moeten ze het oplossen? Ze zitten al sinds 2012 in de problemen. Dat was het laatste jaar dat er een volledige nieuwe line-up van AMD kwam. Bij de R9 2xx waren alleen Tonga en Hawaï nieuw, de rest refresh van oudere chips. Voor de R9 3xx was vrijwel alles een refresh van Tonga of Hawaï, en Fiji was nieuw.

Daarna kwam Polaris 10/11 om alles van Hawai, Tonga, Pitcairn, Bonaire, Curaçao en Cape Verde te vervangen. Er was niet eens een poging meer om hoger te gaan. Dat kwam een jaar later, na alweer een refresh, nu van Polaris met Vega. Waar moeten ze het R&D budget vandaan halen? Ze kunnen niet eens meer een achitectuur naar beneden of boven schalen en afgeleide chips creëren zoals Nvidia altijd doet.

In deze periode kwam Nvidia met een twee generaties Kepler, wat bij elkaar een architectuurgeneratie was, een volle Maxwell generatie, een volle Pascal generatie, en begin volgend jaar Volta. Nu denk ik dat de "Volta" gaming chips in feite grotere en of hoger geclockte Maxwell/Pascal chips zullen zijn met enkele tientallen procenten erbij, puur op clocks, maar dat is al meer dan de RTG kon bereiken doen de afgelopen vijf jaar.

Ik had gisteren trouwens het tweede deel van AdoredTV zijn Nvidia-overzichtje gezien. Man, wat was hij pessimistisch. Ik deel dat pessimisime niet, ik denk dat Navi goede kansen gaat bieden voor AMD als het inderdaad een multi-die GPU wordt en wat betreft de node zal de samenwerking van GF met o.a. Samsung wel vruchten gaan afwerpen. Het kan een paar jaar duren maar ik denk dat AMD wel weer terugkomt en als ik iets heb geleerd over technologie dan is het dat je onmogelijk de verre toekomst kan voorspellen en dat de gekste dingen gebeuren. Wie had het succes van Ryzen verwacht tot 1-2 jaar geleden? Wie had verwacht dat AMD met een veel kleinere GPU Nvidia zo hard zou pakken dankzij de nodeverkleining en een nieuwe architectuur?

Nvidia is geen Intel hé.

Ze vertragen zeker qua prestatieverbeteringen, generatie tot generatie, maar de Maxwell/Pascal is ook gewoon een zeer goede achitectuur voor gaming. Efficiënt, snel, schaalbaar, economisch in productie, wat wil je nog meer? AMD lijkt desondanks alsnog wat voordelen te hebben, zoals iets efficiëntere ROP's, de DSBR, een efficiënte hardware scheduler, snel kunnen switchen tussen graphics en compute berekeningen of toch zeer respectabele prestaties per clock, maar ze kunnen het niet meer omzetten in een echte winnaar, zoals de R9 290(X), maar dan met een goede koeler.

Overigens, die van RX Vega is echt niet zo slecht voor normaal gebruik. Perfect in staat om mijn undervolted RX Vega 56 stil te koelen, onder de 75 graden. Je moet er alleen niet mee overclocken. Nee, 1400MHz core clock aan hitte afvoeren, met minder dan 1000mv, kan die aan, en stil. Dat mijn kaart nu echt behoorlijk richting GTX1080 niveau gaat, en niet eens meer 160W verbruikt is gewoon een gigantische middelvinger naar Nvidia.

De technici van de RTG zijn echt niet slecht, wat ze op technisch presteren is eigenlijk net zo indrukwekkend als Nvidia met haar enorme R&D budget. Dat Vega 10 uberhaupt redelijk kan opboxen tegen GP100, GP102 en GP104 is gewoon uiterst indrukwekkend. Er zit alleen nog meer in GCN, als ze de middelen hebben om er meer uit te halen.

Ik zou niet verbaast zijn als Navi hetzelfde scenario is als Ryzen en hiervoor Bulldozer. Volhouden, enig volume maken en elke cent in R&D gooien voor de grote klapper. Ik onderschat alleen niet wat Navi in zou houden als technische uitdaging, als het echt een schaalbare multiple die chip gaat zijn.

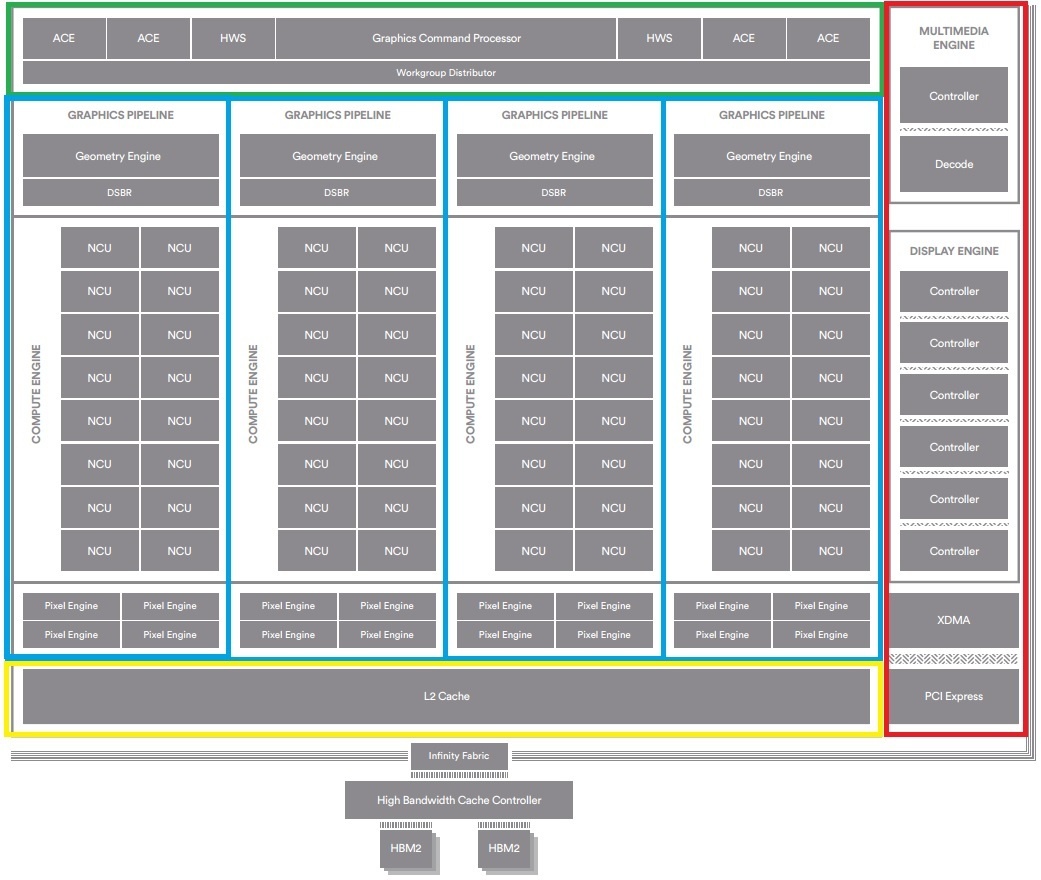

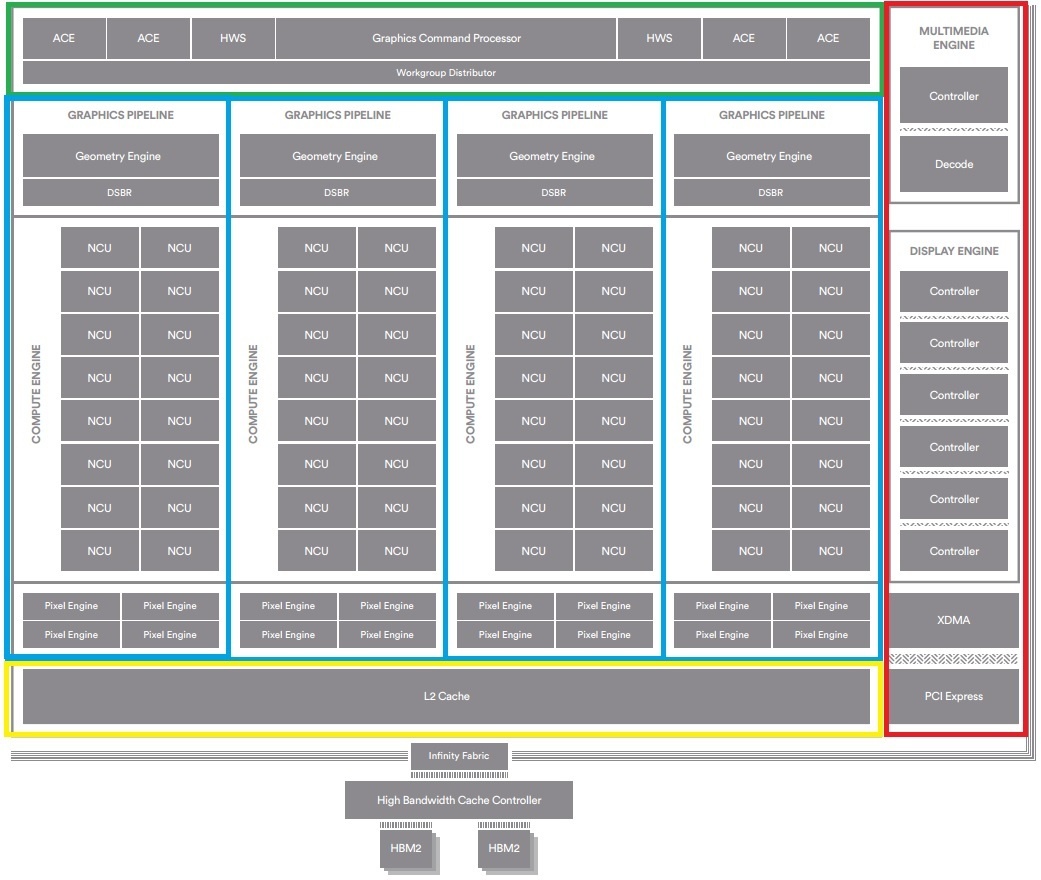

Je kan bij een GPU niet zomaar vier aparte GPU's maken en "aan elkaar lijmen". Als dat kon, dan was Vega denk ik al "gelijmd". Nee, je zal moeten gaan werken met verschillende modulen, deze verbinden en op een interposer zetten. Zou je Vega schaalbaar maken dan zou je denk ik dit krijgen:

Kleurtjes voor wat je allemaal op moet hakken, en apart moet gaan maken.

Kleurtjes voor wat je allemaal op moet hakken, en apart moet gaan maken.

Je hebt een aparte die nodig voor de scheduler, de connecties van de GPU met de rest van de PC zoals PCI-E en I/O, en waarschijnlijk ook de L2 cache. Vervolgens heb je waarschijnlijk ook meerdere aparte Graphics Pipeline dies nodig, zodat je kan schalen. Ideaal gezien heb je hier een of twee typen voor, een puur FP16/FP32, en een speciale FP64 voor HPC taken. Deze moet je kunnen schalen in aantal, dus twee, vier, zes acht etc. Dit is weer een ander probleem omdat GCN tot dusver gelimiteerd was tot vier. Een tijdje terug was er een tweet van een AMD engineer dat dit geen harde limiet is, maar het moet wel ontwikkeld worden. Als je dan toch bezig bent, dan zal er ook wat gedaan moeten worden aan CU vs ROP verhoudingen.

Daarnaast heb je een zeer schaalbare scheduler nodig, en dan kan moet je meerdere L2 cashe dies hebben, of je moet de L2 onboard maken voor de Graphics pipeline die. Dan is het niet meer unified, maar dedicated, en moet je hier met waarden gaan spelen zodat je geen nieuwe bottleneck creëert.

Dit is dan alleen voor zover ik het snap he.

Ik denk dat het nog heel wat complexer is in de praktijk. Er zijn denk ik hele goede redenen waarom dit nog nooit is geprobeerd, het is namelijk nogal een uitdaging dit te creëren zonder latency issues die de prestaties verpesten.

Never argue with an idiot. He will drag you down to his own level and beat you with experience.

Kan wel al opmerken dat hij al wel degelijk 'hoorbaar' is op korte afstand en zeker niet de aller stilste, dus ik neig te zeggen dat Hilbert / Guru zijn beeldvorming aardig klopt. Overigens heeft die van mij een kleine coil whine, dus ik weet niet of dat nog roet in het eten gooit bij A of B.

Kan wel al opmerken dat hij al wel degelijk 'hoorbaar' is op korte afstand en zeker niet de aller stilste, dus ik neig te zeggen dat Hilbert / Guru zijn beeldvorming aardig klopt. Overigens heeft die van mij een kleine coil whine, dus ik weet niet of dat nog roet in het eten gooit bij A of B.:fill(white):strip_exif()/i/2001668195.jpeg?f=thumbmini)

:strip_exif()/i/2001589189.png?f=thumbmini)

:strip_exif()/i/2001589233.png?f=thumbmini)

:fill(white):strip_exif()/i/2001589239.jpeg?f=thumbmini)

:fill(white):strip_exif()/i/2001589243.jpeg?f=thumbmini)

/u/468821/crop594848c6b86e5.png?f=community)

/u/34200/crop6554f56fe2075_cropped.png?f=community)

:strip_exif()/u/233284/crop573f69b75d616.gif?f=community)

:strip_icc():strip_exif()/u/211054/pica.jpg?f=community)

:strip_icc():strip_exif()/u/139806/monitored.jpg?f=community)

:strip_icc():strip_exif()/u/106305/crop5fef6b1a0c373_cropped.jpeg?f=community)

:strip_exif()/u/327460/cowboy.gif?f=community)

:strip_icc():strip_exif()/u/342731/crop55cb221bc1b5c.jpeg?f=community)

/u/324913/crop56a24cce05cd3_cropped.png?f=community)

:strip_exif()/u/211274/bestabstractwallpapers5.gif?f=community)

:strip_icc():strip_exif()/u/291146/crop5d31533862205_cropped.jpeg?f=community)

:strip_icc():strip_exif()/u/45765/3dfx2.jpg?f=community)

/u/400/defember100.png?f=community)

/u/129388/crop59b68a31693d1.png?f=community)

/u/266427/41_2_6060.png?f=community)

/u/180271/av.png?f=community)

/u/343341/crop6095457d39560_cropped.png?f=community)

:strip_icc():strip_exif()/u/451377/crop55c27effefbb4_cropped.jpeg?f=community)