I don't like facts. They have a liberal bias.

Haha lolburne schreef op donderdag 23 augustus 2018 @ 00:35:

[...]

Ik gok dat de dikke DSP in het midden nog even een hartig woordje met je wilt wisselen over de licentievoorwaarden en wat je moet doen om die 4 kHz piep uit je eindmix te halen.

Met die licentie zal het wel loslopen.

Tegenwoordig lijkt het wel een nieuwe hype wat dat betreft.

Menig scopeje dat tegenwoordig niet hackbaar is.

Ik weet eigenlijk niet wat voor terugkoppeling ze tegenwoordig gebruiken bij powersoft?

Een DSP is denk ik niet snel genoeg (althans de ADCs).

Beetje slimme jongen doet zoiets met een FPGA.

Kun je gelijk nog wat noise filters toepassen ed.

Details...burne schreef op donderdag 23 augustus 2018 @ 00:06:

[...]

De dikste K-series is de K20 die 18kW levert. Hoe denk je dat in 1U te doen met een klasse AB-versterker? Of een A-klasse?

(nee, dat is niet PMPO..)

Omdat het klasse-D is kan de kaart de processor vertellen om bv maximaal 25/75% PWM uit te sturen om het vermogen te beperken.B_FORCE schreef op donderdag 23 augustus 2018 @ 00:29:

[...]

Wie heeft het over de kaart kraken?

Het mag duidelijk zijn dat alle spanningen en de nodige stroom aanwezig moet zijn. Kwestie van uitzoeken waar dat geschakeld wordt.

Zoiets zal inderdaad wel gebeuren.memphis schreef op donderdag 23 augustus 2018 @ 09:50:

[...]

Details..., je zult inderdaad heel wat koeling nodig hebben.....

[...]

Omdat het klasse-D is kan de kaart de processor vertellen om bv maximaal 25/75% PWM uit te sturen om het vermogen te beperken.

Of de gain wordt terug geschroefd

Of beiden

Daarom vroeg ik mij al hoe precies de aansturing gaat.

Vaak is het ook niet al te lastig via UART oid bij de firmware te komen via een terminal

Ik verbaas mezelf er iedere keer weer over hoeveel geluidsdruk je met een laag vermogen kan genereren. Tot 10W voldoende voor een film op normaal niveau, 100W/200W een rave en alles daarboven is bloedende oren.B_FORCE schreef op woensdag 22 augustus 2018 @ 22:49:

[...]

Dat vraagt om een hack of bypass.

Bizarre bakken. Ik zit zelf in de audio PA wereld (en ontwerp daar dingen voor).

Zoiets zou nooit mijn keuze zijn om te gebruiken en toe te passen.

Liever gewoon actieve speakers. In de meeste gevallen is 500W-1000W meer dan zat.

(als je het echt slim ontwerpt is 500W vaak al de max en kun je prima uit met 200-300W)

[ Voor 5% gewijzigd door Oyster op 26-08-2018 22:47 ]

Dat ligt er toch maar net aan waar je met je spul staat? Het is nogal een verschil of je in een cafeetje staat of op een openlucht podium. Kun je nog zo "slim" ontwerpen, ligt compleet de situatie.B_FORCE schreef op woensdag 22 augustus 2018 @ 22:49:

Liever gewoon actieve speakers. In de meeste gevallen is 500W-1000W meer dan zat.

(als je het echt slim ontwerpt is 500W vaak al de max en kun je prima uit met 200-300W)

Waarom zou een DSP trager zijn of niet snel genoeg t.o.v. een FPGA? En je kunt toch ook prima filters bouwen in een DSP?B_FORCE schreef op donderdag 23 augustus 2018 @ 00:45:

[...]

Een DSP is denk ik niet snel genoeg (althans de ADCs).

Beetje slimme jongen doet zoiets met een FPGA.

Kun je gelijk nog wat noise filters toepassen ed.

ALS je dat al lukt, kun je misschien aan de gecompileerde firmware komen. Hoe ga je die dan aanpassen zodat je de beperking gaat bypassen?B_FORCE schreef op donderdag 23 augustus 2018 @ 11:03:

[...]

Vaak is het ook niet al te lastig via UART oid bij de firmware te komen via een terminal

Wat betreft snelheid hebben we het over iets anders denk ik.peterkuli schreef op dinsdag 28 augustus 2018 @ 14:53:

[...]

Dat ligt er toch maar net aan waar je met je spul staat? Het is nogal een verschil of je in een cafeetje staat of op een openlucht podium. Kun je nog zo "slim" ontwerpen, ligt compleet de situatie.

[...]

Waarom zou een DSP trager zijn of niet snel genoeg t.o.v. een FPGA? En je kunt toch ook prima filters bouwen in een DSP?

[...]

ALS je dat al lukt, kun je misschien aan de gecompileerde firmware komen. Hoe ga je die dan aanpassen zodat je de beperking gaat bypassen?

Ik heb het over de terugkoppellus van de versterker.

Class-D versterker schakelen ergens tussen de 300kHz en soms zelfs 2Mhz.

Zeker de markt wil naar hogere frequenties ivm kleinere spoelen ed.

Een DSP heeft vaak al een latency van ongeveer 1-20 ms.

Dat gaat dus nooit werken in de terugkoppeling.

Je kunt prima filters bouwen in een DSP, daar zijn ze immers voor.

Wat betreft versterkers hangt het een beetje af van de situatie dat klopt.

Maar aangezien versterker tegenwoordig zo compact en goedkoop zijn, zie ik niet in waarom je het niet mee zou nemen in het ontwerp?

ipv 3 losse prefab bouwsteentjes te gebruiken.. en moeten puzzelen hoe het t beste gaat passen

404 Signature not found

Snel genoeg? Misschien, maar dat laten de benchmarks echter niet zien.mux schreef op dinsdag 28 augustus 2018 @ 15:06:

Iedere cheapo shitty microcontroller is al snel genoeg tegenwoordig... het tijdperk van DSPs voor audiotoepassingen is aardig ver achter ons.

De meeste microcontrollers zijn niet geoptimaliseerd voor DSP topepassingen.

Daardoor krijg je al snel torenhoge delays en latency problemen.

Voor een beetje ontwerp heb je toch wel minstens 10 biquads nodig, of FIR filtering als je het helemaal netjes wil doen.

Buiten het feit dat een ASIC veel goedkoper is in productie.

Je zult dan ook eigenlijk alleen maar DSP IC's zien in audio ontwerpen, never nooit niet een microcontroller voor dezelfde toepassing.

Het merendeel van de fabrikanten gebruikt een vorm van een Sigma DSP van Analog.

[ Voor 7% gewijzigd door B_FORCE op 28-08-2018 17:33 ]

Ik heb toch ook nergens gezegd dat je niet een ontwerp moeten maken? Uiteraard moet dat, daar zijn speciale bureau's voor die niks anders doen. Maar dat jij op voorhand al zegt dat je in de "meeste gevallen" genoeg hebt aan 200 - 300 Watt, is complete nonsens.B_FORCE schreef op dinsdag 28 augustus 2018 @ 17:25:

[...]

Wat betreft versterkers hangt het een beetje af van de situatie dat klopt.

Maar aangezien versterker tegenwoordig zo compact en goedkoop zijn, zie ik niet in waarom je het niet mee zou nemen in het ontwerp?

Heb je hier een link naar de bron o.i.d. van?B_FORCE schreef op dinsdag 28 augustus 2018 @ 17:29:

[...]

Snel genoeg? Misschien, maar dat laten de benchmarks echter niet zien.

Verder op in praatje laten ze toch wel zien dat % CPU usage wel mee lijkt te vallen voor een m4 CPU. Is echter wel voor systeem met maar 2 kanaals op 48kHz. Daarintegen weer helemaal afhankelijk wat je met het audio systeem wilt doen, maar ongetwijfeld zal dat altijd verder "evolueren"

Een DSP heeft meer ALUs, meer data paths met fijnmazigere instructies, meerdere geheugenbanken, en vaak ook ingewikkelde memory modussen zoals indirect addressing met stride (R1+R2*[stride]). Uiteindelijk wel iets meer moeite om een algoritme te mappen met zoveel % hardware utilization. Echter op CPUs heb je vaak die mogelijkheid niet eens. Daar moet bvb fetch, compute, store, inc counter, compare&branch altijd achter elkaar gebeuren. Korte loops op een ARM CPU gaat bijna altijd 2 instructies per iteratie kosten.

Je kan wat spelen met loop unrolling en software pipelining, maar dat is ook zeer eindig (afhankelijk hoeveel registers je hebt..). CPUs zijn gemaakt om general purpose programmaatjes te draaien. Programmaatjes die gemiddeld elke 5 instructies een branch instructie hebben, 40% van hun tijd data aan het verplaatsen zijn, en daardoor zijn CPUs vol worden gepropt met HW om on-the-fly hazards oplossen, branch predictors, pipelines, en caches.

Dat soort technologie zie je in DSPs ook wel terug (eveneens als integer SIMD op ARM Cortex m4+), maar die halen hun kracht met name uit meer rekenhardware en "for good measure" dedicated FIR/IIR/FFT hardware units (zie Analog Devices DSPs). Wat betreft energie efficiëntie zal een DSP met schouders boven een gemiddelde CPU staan.

Als je zoiets uittikt voor een FPGA, heb je het min of meer ook direct voor een ASIC, en kan je zelfs met een goedkope FPGA parallellisatie opschalen tot het belachelijke. Vorig jaar een simpel matrix algoritme ~2000x versneld tussen een ATMEGA328 en een Cyclone V FPGA. Ik schat dat zelfs tussen een pittige ARM Cortex CPU en de FPGA er wel een factor 300 a 400 overeind blijft staan.

Als je het dan ook nog in een functionele HDL doet kan je veel algoritmes waarschijnlijk ook nog eens in paar regeltjes opschrijven

Bron?peterkuli schreef op dinsdag 28 augustus 2018 @ 19:47:

[...]

Ik heb toch ook nergens gezegd dat je niet een ontwerp moeten maken? Uiteraard moet dat, daar zijn speciale bureau's voor die niks anders doen. Maar dat jij op voorhand al zegt dat je in de "meeste gevallen" genoeg hebt aan 200 - 300 Watt, is complete nonsens.

[...]

Heb je hier een link naar de bron o.i.d. van?

Google MIPS en latency in combinatie met DSP en microcontroller.

Speciale bureau, guess what a part of my business is

Anders zou ik ook nooit zo'n statement maken natuurlijk.

@Hans1990

Met een FPGA kan het allemaal, maar ontwikkeling daarvan is vrij langdurig.

Mocht er iemand trouwens zijn die heel goed thuis is met FPGA's ik heb nog een leuk projectje op de plank liggen.

[ Voor 14% gewijzigd door B_FORCE op 28-08-2018 21:01 ]

We praten misschien iets langs elkaar heen, maar... ik vraag me af wat voor micro's je gewend bent? Werk je alleen maar in RTOS-context ofzo? Dan kan ik me voorstellen dat je inconsistente delays krijgt op een general purpose micro.B_FORCE schreef op dinsdag 28 augustus 2018 @ 17:29:

[...]

Snel genoeg? Misschien, maar dat laten de benchmarks echter niet zien.

De meeste microcontrollers zijn niet geoptimaliseerd voor DSP topepassingen.

Daardoor krijg je al snel torenhoge delays en latency problemen.

Voor een beetje ontwerp heb je toch wel minstens 10 biquads nodig, of FIR filtering als je het helemaal netjes wil doen.

Buiten het feit dat een ASIC veel goedkoper is in productie.

Je zult dan ook eigenlijk alleen maar DSP IC's zien in audio ontwerpen, never nooit niet een microcontroller voor dezelfde toepassing.

Het merendeel van de fabrikanten gebruikt een vorm van een Sigma DSP van Analog.

Maar een beetje moderne micro heeft tegenwoordig trucs zoals event bussen, vectored interrupts, floating point logic en hogesnelheids-ADCs en DACs, en lopen bovendien zelf al op 48-72MHz voor het lowend spul, en 288-512MHz voor het iets snellere. Zelfs ADCs/DACs op cortex-m0's zijn tegenwoordig al 300kHz-2MHz. Een FIR filter, of welk lineaire filter je ook wil implementeren, kost misschien 1000 cycles ofzo, zelfs met memory hits. Met groot gemak snel genoeg voor audio.

Audio is takketraag he, je hoeft maar 44kS/s te verwerken. Je hebt een kwart ms een veertigste ms per sample, dat is een eeuwigheid voor moderne micro's. Ik begrijp dat dit misschien lastig is met een 16-bitter of een ARM7, maar vandaag de dag zijn de meeste micro's beter uitgerust dan een TMS320 van 10 jaar geleden. Als je bereid bent bare metal te programmeren is het prima te gebruiken voor audio.

En zelfs een klasse-d versterker implementeren in micro's is al niet zo vreemd meer. Heb ik zelfs in een nog-niet-gelanceerd product gedaan op een AVR XMEGA met behulp van de asynchrone fault events die in die AC/ADC zitten. En dat is een 8-bitter op 48MHz

Er is een verschil tussen wat nodig is en wat de markt wil.mux schreef op dinsdag 28 augustus 2018 @ 21:06:

[...]

We praten misschien iets langs elkaar heen, maar... ik vraag me af wat voor micro's je gewend bent? Werk je alleen maar in RTOS-context ofzo? Dan kan ik me voorstellen dat je inconsistente delays krijgt op een general purpose micro.

Maar een beetje moderne micro heeft tegenwoordig trucs zoals event bussen, vectored interrupts, floating point logic en hogesnelheids-ADCs en DACs, en lopen bovendien zelf al op 48-72MHz voor het lowend spul, en 288-512MHz voor het iets snellere. Zelfs ADCs/DACs op cortex-m0's zijn tegenwoordig al 300kHz-2MHz. Een FIR filter, of welk lineaire filter je ook wil implementeren, kost misschien 1000 cycles ofzo, zelfs met memory hits. Met groot gemak snel genoeg voor audio.

Audio is takketraag he, je hoeft maar 44kS/s te verwerken. Je hebt een kwart ms per sample, dat is een eeuwigheid voor moderne micro's. Ik begrijp dat dit misschien lastig is met een 16-bitter of een ARM7, maar vandaag de dag zijn de meeste micro's beter uitgerust dan een TMS320 van 10 jaar geleden. Als je bereid bent bare metal te programmeren is het prima te gebruiken voor audio.

En zelfs een klasse-d versterker implementeren in micro's is al niet zo vreemd meer. Heb ik zelfs in een nog-niet-gelanceerd product gedaan op een AVR XMEGA met behulp van de asynchrone fault events die in die AC/ADC zitten. En dat is een 8-bitter op 48MHz

Ben het eens dat bepaalde specs onzinnig kunnen klinken, maar in bepaalde gevallen kunnen die best nodig zijn.

Voor professionele audio bijvoorbeeld, met hoog rendement array aan horn drivers heb je aan 16 bits audio niet genoeg.

Dan zul je toch echt minimaal een SNR van 115dB of beter moeten hebben, anders ruist het de pan uit.

Anyway, je begon ermee dat "elke shitty micro" goed genoeg is.

Met een standaard ATTINY of PIC is dit niet te bewerkstelligen, maar ik zie graag het tegendeel.

Als je iets kunt maken dat een SNR heeft van rond de 110dB en THD van beter dan -90dB met een simpele user interface, dan moet je mij even een persoonlijk berichtje sturen.

Dan weet ik namelijk zo honderden klanten.

Dit bedoel ik niet lullig, maar serieus overigens.

Sterker nog, mocht iemand een goed idee hebben om goedkope (!!!) FPGA of microcontroller (minder dan een paar euro) zo te implementeren in een control loop. Serieus PM me.

Je hebt gelijk dat echte highend audio moeilijk wordt in een random MCU. We waren inderdaad langs elkaar aan het praten, want ik zat meer in de trant van consumer audio te denken.

Consumer audio wordt gedicteerd door marketing.mux schreef op dinsdag 28 augustus 2018 @ 21:24:

Damn, dat klinkt nog als een leuke challenge ook... Ik heb er totaal de tijd niet voor, maar ik wed dat het gedaan kan worden.

Je hebt gelijk dat echte highend audio moeilijk wordt in een random MCU. We waren inderdaad langs elkaar aan het praten, want ik zat meer in de trant van consumer audio te denken.

Daar kun je het niet mee eens zijn, maar minder verkoopt niet.

Zul je ook nooit aan de man krijgen.

Maar met 48kHz en 24bit moet je een heel eind komen.

24 bit wordt volgens mij alleen erg lastig?

Mijn probleem is dat dit niet helemaal mijn tak van sport meer is.

Zit meer in de analoge wereld, implementatie en ontwerpen van PCB's (DSP, Class-d power amps ed).

Programmeren laat ik heel graag aan anderen over

Zoals ik al zei, mocht iemand hier er wel serieus ervaring mee hebben, or serieus tijd in wil steken, PM mij.

Kan er zelfs een mooie stage/master opdracht van maken

Dan kun je er daarna altijd nog een stage opdracht van maken.

Een leverancier?jeronimo schreef op dinsdag 28 augustus 2018 @ 22:53:

B_FORCE Zou je zo'n vraagstuk niet beter bij een leverancier neer kunnen leggen. Ik denk zo maar dat medetweaker @kdeboois je wel verder zou kunnen helpen. In ieder geval met het vraagstuk of de performance van de FPGA en de gewenste kostprijs in hetzelfde speelveld liggen.

Dan kun je er daarna altijd nog een stage opdracht van maken.

Snap niet zo goed wat een leverancier ermee te maken heeft?

Ik heb zelf een bedrijf dus qua levering van dingen moet dat wel goed komen.

Of doel je de fabrikanten van dergelijks IC's?

Dat heb ik al meerdere keren gedaan, raak je in een groot marketing bos zonder enige concrete verhalen.

De reden waarom er vraag is naar oplossingen is omdat bepaalde mensen een patent hebben op een bepaalde manier van terugkoppelen (dat zoiets kan, maar goed).

Daardoor is het aantal mogelijkheden zeer beperkt.

Ik weet zelf behoorlijk goed wat er met FPGA's mogelijk is (nogmaals als een microcontroller het zou kunnen nog liever, stuk goedkoper), maar mis net even de kennis welke "specs" en parameters nodig zullen zijn.

[ Voor 6% gewijzigd door B_FORCE op 28-08-2018 23:30 ]

Leveranciers hebben Field Application Engineers in dienst die daar mee kunnen helpen. Zoals ik, voor FPGA vragen of een goede doorverwijzing als FPGA niet zinnig is en er beter een microcontroller in kan.B_FORCE schreef op dinsdag 28 augustus 2018 @ 23:28:

[...]

Een leverancier?

Snap niet zo goed wat een leverancier ermee te maken heeft?

Ik heb zelf een bedrijf dus qua levering van dingen moet dat wel goed komen.

Of doel je de fabrikanten van dergelijks IC's?

Dat heb ik al meerdere keren gedaan, raak je in een groot marketing bos zonder enige concrete verhalen.

De reden waarom er vraag is naar oplossingen is omdat bepaalde mensen een patent hebben op een bepaalde manier van terugkoppelen (dat zoiets kan, maar goed).

Daardoor is het aantal mogelijkheden zeer beperkt.

Ik weet zelf behoorlijk goed wat er met FPGA's mogelijk is (nogmaals als een microcontroller het zou kunnen nog liever, stuk goedkoper), maar mis net even de kennis welke "specs" en parameters nodig zullen zijn.

PSN: LoadedBaton XBL: LoadedBaton

Zoals ik al zei, alleen nog maar vastgelopen bij leveranciers.kdeboois schreef op woensdag 29 augustus 2018 @ 00:41:

[...]

Leveranciers hebben Field Application Engineers in dienst die daar mee kunnen helpen. Zoals ik, voor FPGA vragen of een goede doorverwijzing als FPGA niet zinnig is en er beter een microcontroller in kan.

Maar brand los zou ik zeggen

Als het over een closed loop feedback gaat in FPGA dan wordt er meestal een sigma delta converter gebruikt waarbij de modulator dicht bij de power stage (vaak ook geisoleerd) een 1 bit data stream van het analoge signaal maakt. In de FPGA kan je dan uit die ene data stream een overbelastings beveiliging maken en een daadwerkelijk feedback loop.B_FORCE schreef op woensdag 29 augustus 2018 @ 00:49:

[...]

Zoals ik al zei, alleen nog maar vastgelopen bij leveranciers.

Maar brand los zou ik zeggen

Wordt veel in drives (high end motorcontrollers) gebruikt en daar zijn de modulatoren ook voor gemaakt door bijvoorbeeld Broadcom (Ex Avago, Ex Agilent, Ex HP) zoals deze

Met de FPGA kan de je rest van de sigma delta converter opbouwen en volledig naar wens op bouwen. Alle FPGA fabrikanten bouwen hier voornamelijk motor controls mee in hun application notes, maar een high end audio versterker moet ook prima kunnen.

PSN: LoadedBaton XBL: LoadedBaton

Thanks.kdeboois schreef op woensdag 29 augustus 2018 @ 09:09:

[...]

Als het over een closed loop feedback gaat in FPGA dan wordt er meestal een sigma delta converter gebruikt waarbij de modulator dicht bij de power stage (vaak ook geisoleerd) een 1 bit data stream van het analoge signaal maakt. In de FPGA kan je dan uit die ene data stream een overbelastings beveiliging maken en een daadwerkelijk feedback loop.

Wordt veel in drives (high end motorcontrollers) gebruikt en daar zijn de modulatoren ook voor gemaakt door bijvoorbeeld Broadcom (Ex Avago, Ex Agilent, Ex HP) zoals deze

Met de FPGA kan de je rest van de sigma delta converter opbouwen en volledig naar wens op bouwen. Alle FPGA fabrikanten bouwen hier voornamelijk motor controls mee in hun application notes, maar een high end audio versterker moet ook prima kunnen.

Tot dusver is mij dit al bekend, ook dat het mogelijk moet zijn.

Mijn vraag is meer wat er minimaal voor nodig is qua specs ed voor een systeem dat tussen 300kHz en 2Mhz schakelt?

(Hoeveel cels snelheid ed)

Ook of het dus evt met een ucontroller kan.

De modulator werkt op 10 MHz en normaliter gaat dat met de goedkoopste en kleinste FPGA. Een Spartan 7 of een Zynq 7000 zeg ik dan met mijn huidige pet op.B_FORCE schreef op woensdag 29 augustus 2018 @ 11:14:

[...]

Thanks.

Tot dusver is mij dit al bekend, ook dat het mogelijk moet zijn.

Mijn vraag is meer wat er minimaal voor nodig is qua specs ed voor een systeem dat tussen 300kHz en 2Mhz schakelt?

(Hoeveel cels snelheid ed)

Ook of het dus evt met een ucontroller kan.

Zullen we een keer bellen om de mogelijkheden door te spreken of wil je het hier verder doen ? Mij om het even.

PSN: LoadedBaton XBL: LoadedBaton

Voor mij ook om het even. Misschien wel leuk om zo'n proces te delen?kdeboois schreef op woensdag 29 augustus 2018 @ 11:51:

[...]

De modulator werkt op 10 MHz en normaliter gaat dat met de goedkoopste en kleinste FPGA. Een Spartan 7 of een Zynq 7000 zeg ik dan met mijn huidige pet op.

Zullen we een keer bellen om de mogelijkheden door te spreken of wil je het hier verder doen ? Mij om het even.

Kunnen mensen misschien nog wat van leren.

Kan me alleen voorstellen dat het misschien wel erg veel info wordt.

Ik stuur je wel een PM.

Zien er iig niet uit als goedkope alternatieven

[ Voor 4% gewijzigd door B_FORCE op 29-08-2018 12:20 ]

Het is niet enkel de manier van terugkoppelen waar een patent op ligt. Het gaat ook om de manier waarop de terugkoppeling geïntegreerd wordt (kan worden) in de control-loop. De integratie van het systeem als geheel wordt versimpeld. Dat is een interessante vinding. Ik heb nog ergens betere pdfs over dit onderwerp, maar ik kan ze even niet vinden.B_FORCE schreef op dinsdag 28 augustus 2018 @ 23:28:

[...]

De reden waarom er vraag is naar oplossingen is omdat bepaalde mensen een patent hebben op een bepaalde manier van terugkoppelen (dat zoiets kan, maar goed).

Daardoor is het aantal mogelijkheden zeer beperkt.

Ik ben bekend met het verhaal hierachter (en de papers en patenten).Oyster schreef op woensdag 29 augustus 2018 @ 12:03:

[...]

Het is niet enkel de manier van terugkoppelen waar een patent op ligt. Het gaat ook om de manier waarop de terugkoppeling geïntegreerd wordt (kan worden) in de control-loop. De integratie van het systeem als geheel wordt versimpeld. Dat is een interessante vinding. Ik heb nog ergens betere pdfs over dit onderwerp, maar ik kan ze even niet vinden.

Het is echter een feit dat daardoor de rest nogal in de knoop zit.

Het is eigenlijk een nogal voor de hand liggende techniek dat al vrij oud is.

Toevallig toegepast in audio.

Heb er weleens een jurist naar laten kijken, die vond het ook enigszins discutabel.

Maar goed dat is niet ongewoon bij patenten.

FPGA prijzen zijn altijd wat hoger versus een volledige kant-en-klare oplossing, maar als je er daarvan meerdere nodig hebt is een FPGA vanwege de integratie mogelijkheid zeer flexibel en soms zelfs goedkoper.B_FORCE schreef op woensdag 29 augustus 2018 @ 11:55:

[...]

Voor mij ook om het even. Misschien wel leuk om zo'n proces te delen?

Kunnen mensen misschien nog wat van leren.

Kan me alleen voorstellen dat het misschien wel erg veel info wordt.

Ik stuur je wel een PM.

Zien er iig niet uit als goedkope alternatieven

De kleinste Spartan 7 kunnen we leveren voor zo'n 10 Euro per stuk en bij grotere aantallen gaat die prijs met 10-tallen procenten naar beneden.

Voor de motor control toepassing heeft Xilinx i.i.g. een serie video's gemaakt en een voorbeeld design met een powerstage. Deze video gaat in op het maken van de feedback loop en de snelheden vs DSP en microcontroller.

Bij deze link geven ze wat resource getallen voor een audio toepassing uit een universitair onderzoek naar een FPGA gebaseerde klasse D versterker.

In microcontroller land ken ik alleen TI met zijn C2000 Delfino die in de buurt komt van feedback loops op die snelheden. Digikey heeft een stukje geschreven om de twee te vergelijken.

In prijs zijn deze devices te vergelijken met een kleine FPGA. Dus als je echt onder de paar Euro uit wil komen, zul je concessies moeten doen.

[ Voor 19% gewijzigd door kdeboois op 01-09-2018 11:14 . Reden: aanvulling ]

PSN: LoadedBaton XBL: LoadedBaton

[ Voor 16% gewijzigd door Oyster op 02-09-2018 10:47 ]

Hell yeah!Oyster schreef op zondag 2 september 2018 @ 10:43:

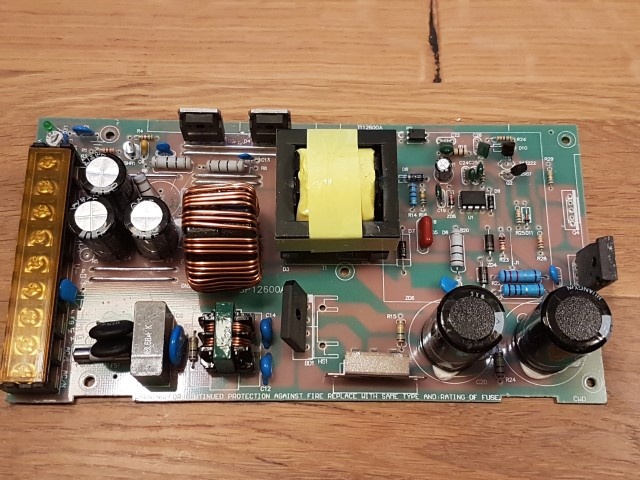

Ik ga één Powersoft K6 scrappen. Zijn er liefhebbers die behoefte hebben aan een gedetailleerde teardown?

[afbeelding]

Zet het op youtube, en je krijgt vast een hoop views!

[ Voor 8% gewijzigd door Gwannoes op 02-09-2018 13:23 ]

Hmmz, hier komt dus m'n sig

Uiteraard altijd.Oyster schreef op zondag 2 september 2018 @ 10:43:

Ik ga één Powersoft K6 scrappen. Zijn er liefhebbers die behoefte hebben aan een gedetailleerde teardown?

[afbeelding]

Er is geen betere leerschool dan te kijken wat de anderen doen

Hoewel Powersoft volgens mij dedicated half bridge drivers gebruikt?

@kdeboois

De link naar dat onderzoek werkt niet.

10 euro is pittig veel, daar moet dan ook nog een gate/half bridge driver bij.

Neem aan dat zo'n Spartan 7 wel een fatsoenlijke ADC aan boord heeft?

Volgens mij mag je gewoon backward engineering en je eigen schema maken?Oyster schreef op zondag 2 september 2018 @ 14:47:

Oke, ik ga even een plannetje maken om het enigszins sjiek te documenteren. Als iemand geinteresseerd is in een specifiek onderwep zoals bijvoorbeeld smps, powerstage, dsp, smartcard, etc stuur mij dan even een dm. Ik sta ervoor open om hem in groepsverband uit te kleden. Heeft iemand enig idee hoeveel er geopenbaard kan worden voordat het juridisch mogelijk problematisch wordt?

Normaliter vallen schema's onder gewone copyrights, maar je maakt je eigen dus dat is geen issue.

De techniek valt onder een patent dus is daarmee covered.

Op EEVBlog gebeurt dit dan ook constant.

Meest interessante vind ik persoonlijk altijd PCB design

Vreemd, hier wel.B_FORCE schreef op zondag 2 september 2018 @ 14:02:

[...]

De link naar dat onderzoek werkt niet.

10 euro is pittig veel, daar moet dan ook nog een gate/half bridge driver bij.

Neem aan dat zo'n Spartan 7 wel een fatsoenlijke ADC aan boord heeft?

De Spartan 7 is in de set-up die ik voorstel de ‘D’ in de ADC. De modulator is de ‘A’ en samen vormen ze de ADC

PSN: LoadedBaton XBL: LoadedBaton

IAF staat voor Institute of Applied Flansing

www.frees-it.com

Mitsubishi externe temperatuur sensor (Home Assistant compatible): V&A - ClimaControl - Ook voor Panasonic & LG.

After the first glass you see things as you wish they were. After the second you see things as they are not. Finally you see things as they really are, and that is the most horrible thing in the world...

Oscar Wilde

Voron V0.2 | Prusa Core One+ | E3CNC rodmod (in progress)

Ik ben op zoek naar behuizingen voor wat projectjes. Bij conrad verkopen ze dit soort dingen (zie hieronder). Weet iemand waar ik deze nog meer kan kopen, gewoon in een reguliere winkel?

https://www.conrad.nl/p/w...h=1&vat=true&insert_kz=8J

Weet iemand een (electronica onderdelen) winkel in de buurt van Zeist waar ze ook projectbehuizingen verkopen?

Ik wil niet te brutaal overkomen maar ooit van de Gouden Gids gehoord? En ook met Google vind je elektronicawinkels in de buurt, er zit er zelfs 1 in Zeist zag ik. Een beetje eigen inzet mag ook best wel.PietjePuk schreef op zondag 9 september 2018 @ 09:51:

Daarvan ken ik er maar een handjevol die minstens 50 kilometer bij mijn woonplaats vandaan liggen. Misschien moet ik de vraag iets concreter stellen:

Weet iemand een (electronica onderdelen) winkel in de buurt van Zeist waar ze ook projectbehuizingen verkopen?

Als je de verzendkosten wilt onlopen kan je natuurlijk ook Ebay, Banggood, Aliexpress etc raadplegen als ook de Conrad boven de 35 euro gratis verzend.

Switch voltage 2.5-30v DC

Max switch current 10mA

puls width ~100ms

resistence open > 120Mohm

resistence closed < 6ohm

Bij 500mV werkt deze gewoon en alles boven de 500mV gaat de CC (@ 5mA) aan.

Dus hoe kan ik zorgen dat ik deze puls op normale manier kan verwerken zodat een sensor versterker hier wat aan heeft.

DSO138 (beter iets dan niets

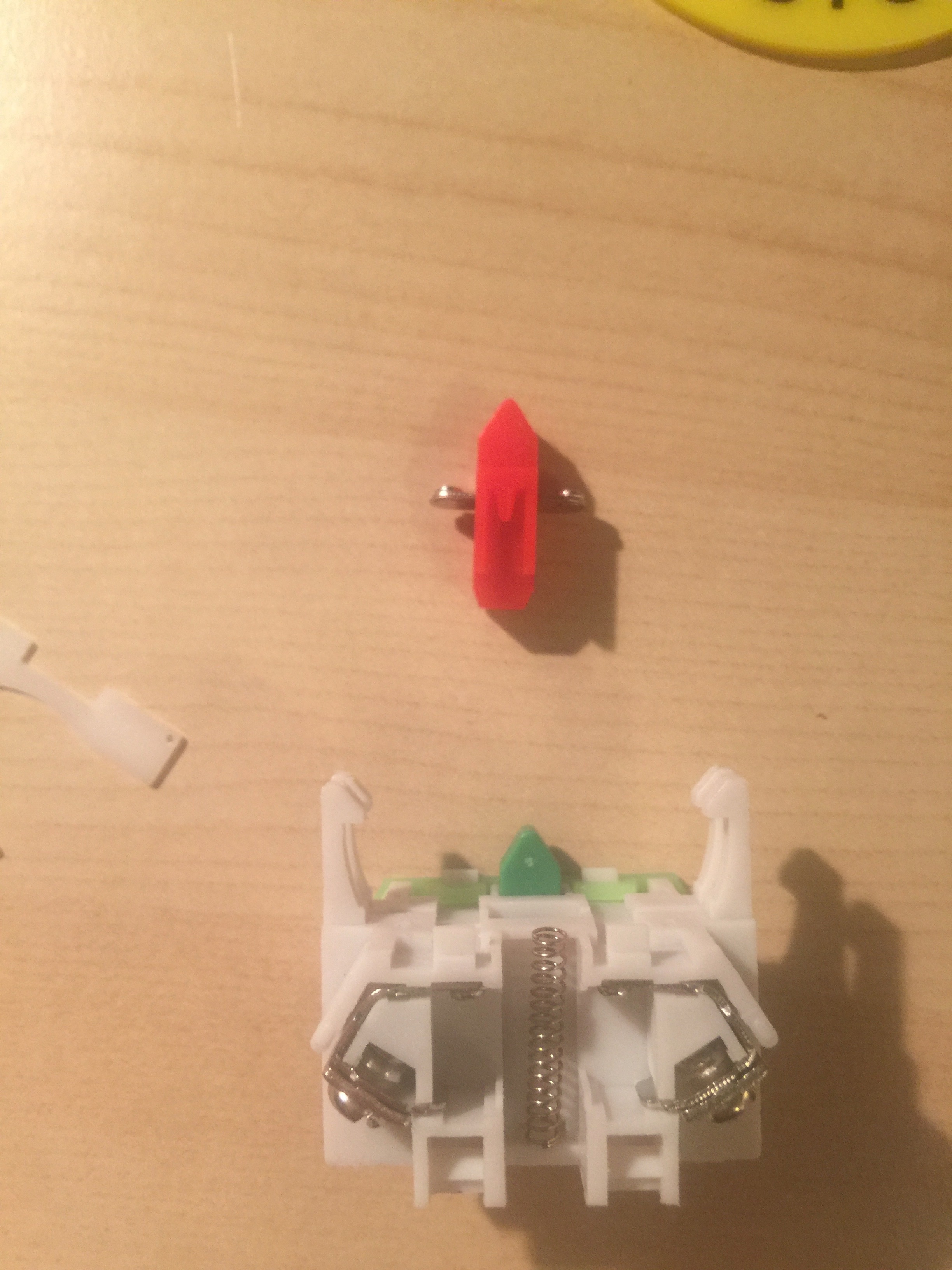

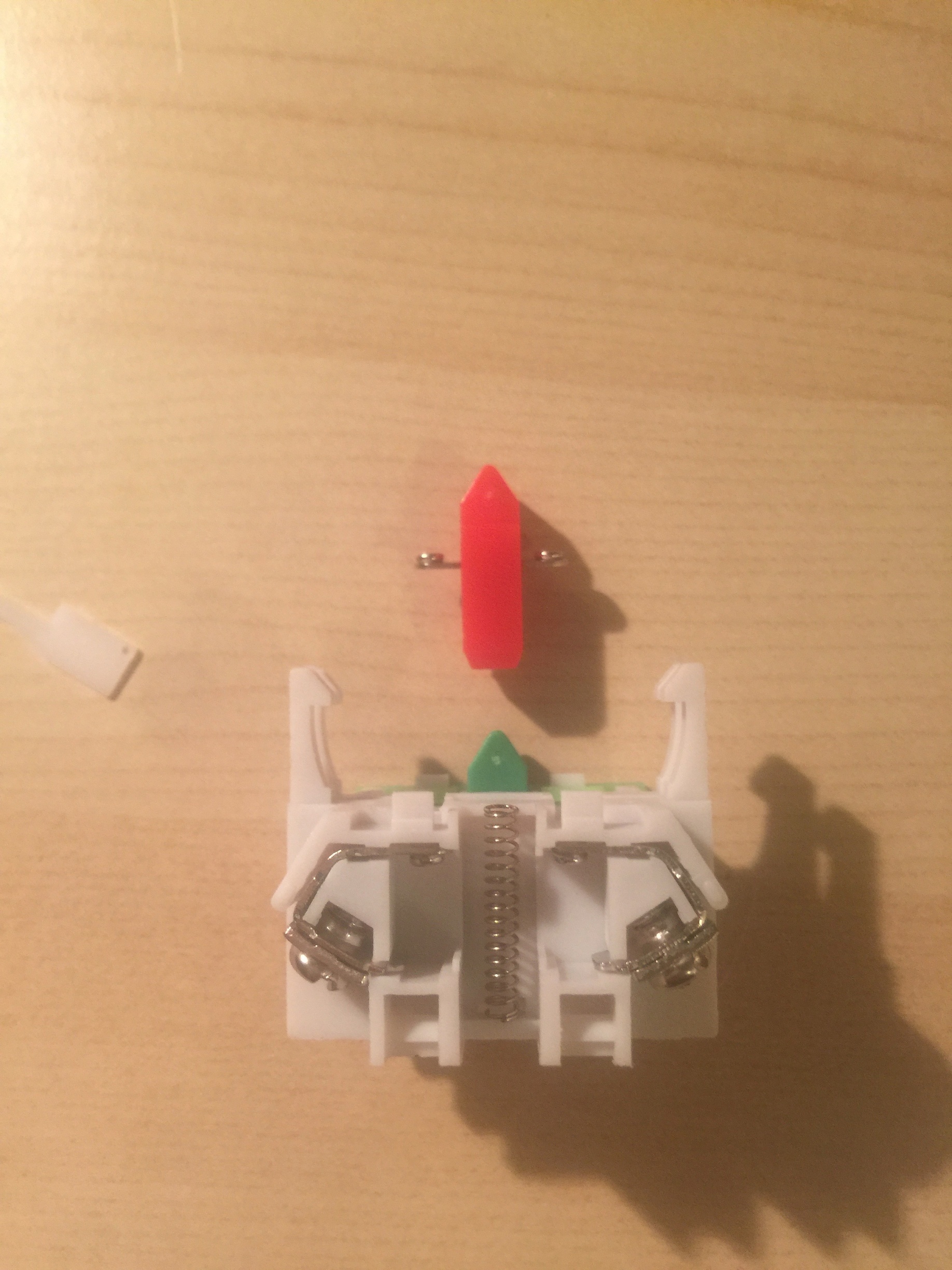

Voor de controlekast heb ik een Nood stop besteld. Deze koste mij iets van 3 a 4 dollar. Ik vond het wel geinig om hem even open te maken om te zien hoe veilig dit ding nou echt is. Ik twijfel toch wel over de veiligheid haha, het is allemaal wel zwak plastic.

Nu zit er in de binnenkant een normally closed schakelaar. Hij verbind dus altijd door zie foto:

Ik dacht dus, als het knop gedeelte faalt en kapot gaat, en je weet dat niet, dan schakelt hij hem dus niet uit. Dan werkt je noodstop in eens niet meer. Dan moet toch juist die noodknop ook inschakelen?

Al wat ik aanraak werk niet meer zoals het hoort. Damic houd niet van zijn verjaardag

Op wikipedia gekeken, en daar zie ik iets staan (https://en.wikipedia.org/wiki/Safety_relay) Dat ze een specifieke functie hebben, en dus daar alleen voor ontworpen.Damic schreef op zondag 9 september 2018 @ 21:51:

@jctjepkema normaal is een noodstop circuit met 2 NC schakelaars (redundant) en zit ie aangesloten op een PILZ relais (kost wel wat, maar industrie standaard) soms word er ook wel eens een gewone hulp relais gebruikt maar dan nog altijd met 2 NC contacten die in serie staan.

Ik vind het dan zo raar dat wanneer dat knop gedeelte, daar zit het indrukken en draai gedeelte in, faalt, de contact punten hem dan aan blijven houden. dat is toch dom?

Al wat ik aanraak werk niet meer zoals het hoort. Damic houd niet van zijn verjaardag

Kijkvoer:jctjepkema schreef op zondag 9 september 2018 @ 21:27:

Ik ben al een tijdje bezig om een CNC te bouwen. Ik heb uit Duitsland via Aliexpress een kant en klaar frame gekocht en voeg daar zelf de motoren, motor drivers, controller limit switches etc aan toe voegen.

Sowieso is Bigclivedotcom een aanrader.

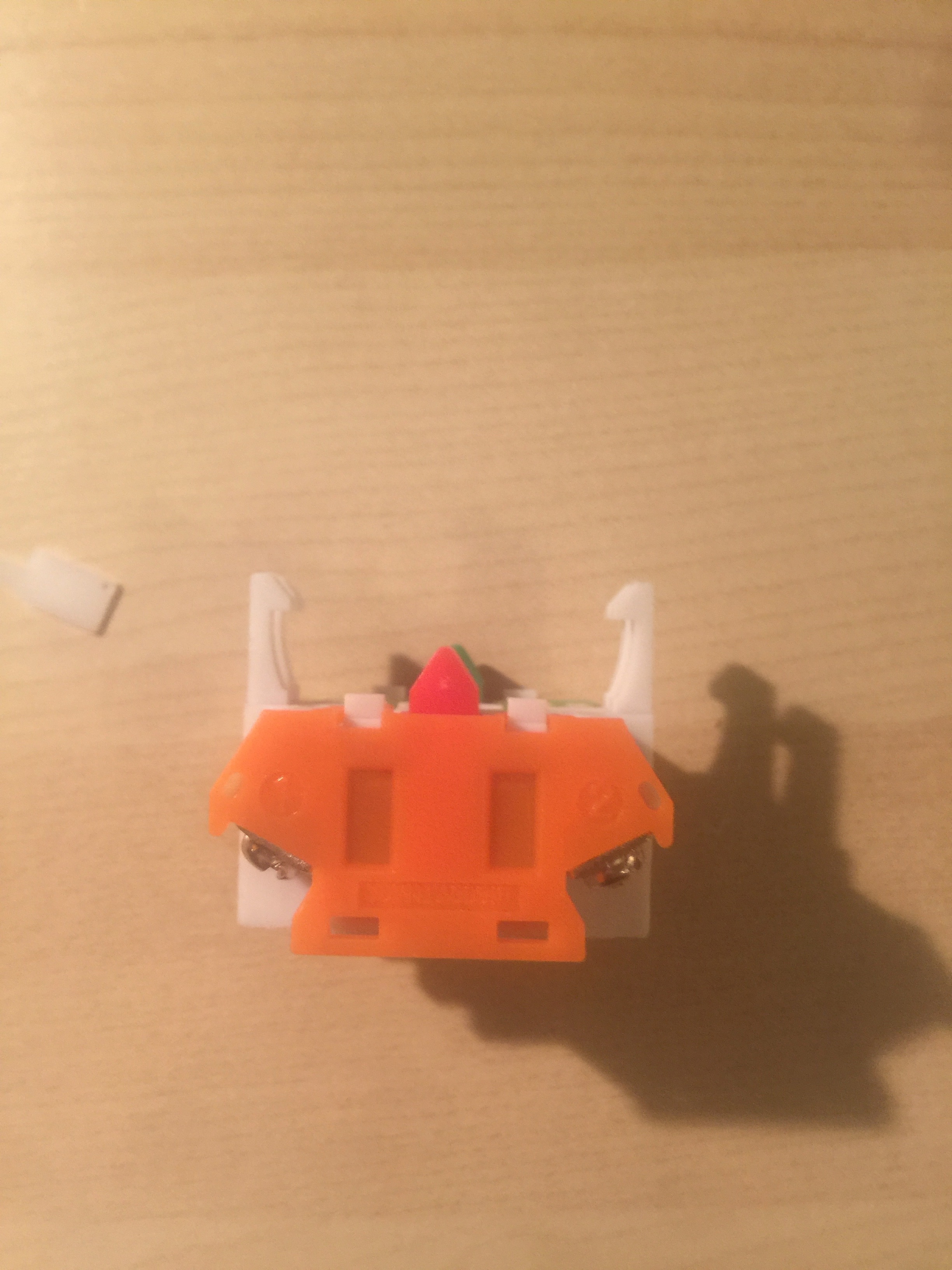

Grappig exact dezelfde knop als ik heb. Wat me wel opvalt is dat hij hem bij het in elkaar zetten monteert als Normally Open, en ik als Normally Closed.Roamor schreef op maandag 10 september 2018 @ 08:01:

[...]

Kijkvoer:

[video]

Sowieso is Bigclivedotcom een aanrader.

EDIT:

Ik kijk nog eens goed, en het blijkt dus de oranje die NC is en de Groene die Normally Open is! Verder voelt die knop op zich wel prima aan. Ik kom vanzelf wel een keer een "duurdere" tegen die ik ga monteren

[ Voor 21% gewijzigd door jctjepkema op 10-09-2018 08:50 ]

Ik heb echt alleen maar problemen met de website van Farnell.JDTeunis schreef op woensdag 12 september 2018 @ 12:48:

*gaap* farnell is weer eens zo langzaam dat alle loads een time-out geven. Het wordt eens tijd dat een andere leverancier ook gratis gaat verzenden, dan stap ik direct over.

Vooral 's avonds en in het weekend

Hoe zit het tegenwoordig met invoerkosten ed?JDTeunis schreef op donderdag 13 september 2018 @ 08:50:

Ik heb besloten om voortaan maar Digikey te gebruiken. Kun je tenminste normaal zoeken (zeker met dit script, aanrader! https://www.digikey.com/e...serscript+for+Digikey.com ). Betaal je wel 25 euro verzendkosten maar bespaart me makkelijk een half uur gemiste productiviteit.

Er is uiteraard ook nog Mouser.

Ik gebruik zelf elpro.org ook nog weleens

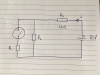

Ik probeer het op te lossen met een voltage-deler oplossing maar ik kom er niet uitThaHandy schreef op zondag 9 september 2018 @ 19:15:

Ik heb hier een wiegand sensor en ik ben al een tijde aan het google wat het wiegand effect nou inhoud en hoe ik deze kan aansluiten op een sensor versterker (NAMUR oid.)

Switch voltage 2.5-30v DC

Max switch current 10mA

puls width ~100ms

resistence open > 120Mohm

resistence closed < 6ohm

Bij 500mV werkt deze gewoon en alles boven de 500mV gaat de CC (@ 5mA) aan.

Dus hoe kan ik zorgen dat ik deze puls op normale manier kan verwerken zodat een sensor versterker hier wat aan heeft.

DSO138 (beter iets dan niets)

[Afbeelding]

Ik heb hier een NAMUR-sensor versterker welke op 8a9v / 8mA werkt, maar met een sensor die op 0.5v/5mA juist werkt

Volgens de formule zou ik 0.47v 0.436 moeten krijgen op de sensor. maar als ik sensor zo aansluit meet ik 0.55v (max="kortsluiting") en het andere deel is 2.5v. Daarnaast het probleem is dat wanneer de sensor een puls maakt(zover ben ik nog niet), deze kortsluit en er geen 0.5v op de sensor komt.

Wat ik probeer te bereiken is dat de sensor altijd <0.5v krijgt ongeacht deze even is kortgesloten(liever een lager dan een te hoge voltage). Namur principe kan aangehouden worden maar de versterker werkt ook gewoon met een simpele schakelaar principe.

/edit

Ik zie dat ik de 10k en de 560 heb omgedraaid. moment...

/edit 2

Ik kom er niet uit. Ik heb 10k nodig minimaal nodig voor "open" signaal, maar hier kan ik geen voltage-deler van maken zetten omdat deze dan 10k en 560ohm totaal is. andersom 180k en 10k is het nog erger.

Help

[ Voor 9% gewijzigd door ThaHandy op 15-09-2018 15:21 ]

Digikey is wat mij betreft op dit moment de beste. Beste en snelste parametric search, grootste aanbod en - ok niet next business day maar toch - prima levertijden. Boven €50 gratis verzenden, invoerrechten betaald en als je werk er enigszins een planning op na houdt is 2 werkdagen shipping echt prima te doen. Oh en ze hebben zelfs een NL telefoonnummer met Nederlandse werknemers tegenwoordig.JDTeunis schreef op donderdag 13 september 2018 @ 08:50:

Ik heb besloten om voortaan maar Digikey te gebruiken. Kun je tenminste normaal zoeken (zeker met dit script, aanrader! https://www.digikey.com/e...serscript+for+Digikey.com ). Betaal je wel 25 euro verzendkosten maar bespaart me makkelijk een half uur gemiste productiviteit.

Ga alleen nog naar Farnell voor klein grut dat ik echt zsm nodig heb. Wel jammer want vroeger waren de rollen omgedraaid...

Ik ben niet echt bekend met dit soort systemen, maar als ik het goed begrijp probeer je een willekeurige sensor aan te sluiten op een module voor NAMUR-sensoren. Jouw sensor kent maar 2 states: open (> 120Mohm) en closed (< 6ohm).ThaHandy schreef op zaterdag 15 september 2018 @ 13:47:

Ik probeer het op te lossen met een voltage-deler oplossing maar ik kom er niet uit

Volgens Wikipedia zijn er blijkbaar vier situaties te onderscheiden, afhankelijk van de stroom die er loopt door de sensor. Je moet dus zorgen dat jij hier aan voldoet. Ten opzichte van jouw schema is het makkelijker om de weerstanden voor open en gesloten toestand los van elkaar te kunnen kiezen. Dat kan bijvoorbeeld zo (klikbaar):

Edit: mijn schema hoeft niet direct ander gedrag op te leveren, maar het maakt naar mijn idee debuggen en waardes kiezen makkelijker.

Een probleem waar je misschien tegenaan loopt is dat je de minimale voedingsspanning voor jouw sensor (2,5 volt) niet onder alle omstandigheden kunt garanderen. Afhankelijk van hoe de sensor geïmplementeerd is, kan dat ongewenst gedrag geven. Is dat inderdaad het geval, dan moet je misschien verder kijken dan alleen een weerstandsnetwerkje.

[ Voor 23% gewijzigd door Comp-Freak op 16-09-2018 19:07 ]

Goed om te weten dat ze tegenwoordig invoerkosten op zich nemen.Genoil schreef op zaterdag 15 september 2018 @ 21:06:

[...]

Digikey is wat mij betreft op dit moment de beste. Beste en snelste parametric search, grootste aanbod en - ok niet next business day maar toch - prima levertijden. Boven €50 gratis verzenden, invoerrechten betaald en als je werk er enigszins een planning op na houdt is 2 werkdagen shipping echt prima te doen. Oh en ze hebben zelfs een NL telefoonnummer met Nederlandse werknemers tegenwoordig.

Ga alleen nog naar Farnell voor klein grut dat ik echt zsm nodig heb. Wel jammer want vroeger waren de rollen omgedraaid...

Voor ontwikkeling is een paar dagen met een goede planning meestal geen probleem.

Enkel in productie is het wat lastig.

NAMUR-weerstandsnetwerk had ik gezien, maar kom er net achter waarom de sensor niet werkte....Comp-Freak schreef op zondag 16 september 2018 @ 18:52:

[...]

Ik ben niet echt bekend met dit soort systemen, maar als ik het goed begrijp probeer je een willekeurige sensor aan te sluiten op een module voor NAMUR-sensoren. Jouw sensor kent maar 2 states: open (> 120Mohm) en closed (< 6ohm).

Volgens Wikipedia zijn er blijkbaar vier situaties te onderscheiden, afhankelijk van de stroom die er loopt door de sensor. Je moet dus zorgen dat jij hier aan voldoet. Ten opzichte van jouw schema is het makkelijker om de weerstanden voor open en gesloten toestand los van elkaar te kunnen kiezen. Dat kan bijvoorbeeld zo (klikbaar):

[Afbeelding: schema2]

Edit: mijn schema hoeft niet direct ander gedrag op te leveren, maar het maakt naar mijn idee debuggen en waardes kiezen makkelijker.

Een probleem waar je misschien tegenaan loopt is dat je de minimale voedingsspanning voor jouw sensor (2,5 volt) niet onder alle omstandigheden kunt garanderen. Afhankelijk van hoe de sensor geïmplementeerd is, kan dat ongewenst gedrag geven. Is dat inderdaad het geval, dan moet je misschien verder kijken dan alleen een weerstandsnetwerkje.

Meten is weten.

Sluit ik de sensor direct aan, met de correct polariteit, werkt deze gewoon

Verwijderd

- Ik heb deze common anode RGB LEDs, dus voor LED_RAGB heb ik LED_THT:LED_D5.0mm-4 geselecteerd, wat denk ik wel klopt.

- Voor Conn_01x05 denk ik dat ik Connector_PinHeader_2.54mm:PinHeader_1x05_P2.54mm_Vertical moet selecteren als ik er zo iets op wil solderen.

- Voor R weet ik het niet zo goed en heb ik nu Resistor_THT:R_Axial_DIN0207_L6.3mm_D2.5mm_P7.62mm_Horizontal geselecteerd, omdat dat de eerste was waar 1/4W bij staat en ik heb deze weerstandjes (220 Ohm als dat iets uitmaakt).

- Qua 74HC595 heb ik de SN74HC595N, welke een PDIP package heeft met 16 pinnen, dus heb ik Package_DIP:DIP-16_W7.62mm geselecteerd, maar ik weet niet of dat de goede optie is.

Klopt dat allemaal?

Edit: en hoe moet ik alles exporteren in pcbnew als ik het bij Elecrow wil printen?

[ Voor 3% gewijzigd door Verwijderd op 19-09-2018 19:17 ]

Ik wil bijvoorbeeld de microcontroller van de Arduino Nano (atmega328p-au) integreren in mijn pcb. Ik heb de officiele opensource documenten gevonden van Arduino zelf, daar staat oa de microcontroller in, maar ik kan dit ene component niet exporteren voor eigen gebruik. Heeft iemand een idee hoe ik dit kan oplossen?

Thanks!

To import your new library into EAGLE:

1. Start EAGLE.

2. Select File -> New -> Library from the menu.

3. In the blank library window, select File -> Script from the menu.

4. Select the EDIT tab.

5. Browse to the correct EAGLE Script file (".scr" file extension) in the file "Open" window.

6. After opening the file, the script will populate the new library.

7. Use File -> Save (or Save As..) to save the library to the desired location in EAGLE native format.

[ Voor 10% gewijzigd door jeronimo op 18-09-2018 20:51 ]

net even een naafdynamo in opnieuw gewikkeld ( draad was gebroken bij de as, en nu dus 1 slag minder op de spoel ) en werkt ze inmiddels weer..

alleen zette het mij aan het denken.. er kan meer draad op de spoel..

meer draad (bij de zelfde draaddikte) zou een hogere spanning leveren

bij een dikkere draad (van de zelfde lengte als de huidige...) zou het vermogen omhoog gaan right?

nou ben ik lekker handig geweest door niet te meten hoelang of welke draaddikte er op zit k weet niet handig

is dit misschien uit te rekenen?

404 Signature not found

Maar wat zou je met meer spanning/vermogen moeten?

en meer spanning bij het zelfde uitgangs vermogen zou ideaal zijn.. gezien het door een brugcell gaat en daarna naar een buckboost om het netjes op 13.6V te brengen.. kost energie

gezien de 6V wisselspanning na het gelijkrichten nog lange geen 13.6V is zou een hogere spanning de verliezen wat kunnen compenseren...

404 Signature not found

Edit: http://pilom.com/BicycleElectronics/DynamoCircuits.htm

Dit is een hele interessante site over fietsdynamo's.

[ Voor 14% gewijzigd door marcop23 op 22-09-2018 22:15 ]

het toerental is gelijk aan die van het hele wiel.. ipv een factor tig meer wat een banddynamo doet

404 Signature not found

Met een speciale laag-ohm bereik meter meten en dan een stukje van een meter meten en hoppa, 2 getallen waar je iets mee kanSMSfreakie schreef op zaterdag 22 september 2018 @ 21:16:

nou ben ik lekker handig geweest door niet te meten hoelang of welke draaddikte er op zit k weet niet handig

is dit misschien uit te rekenen?

https://www.ledstripxl.nl...eding-20-ampere-500w.html

Bedrag is bijna te mooi om waar te zijn. Maar omdat het maar 24V is gaat er toch al best wat A lopen dus ik dacht dit is een goeie optie. + hij is mooi weg te werken straks op het plankje waar ik hem op wil gaan monteren.

Is dit wat? Of zijn er goede alternatieven zoals 2e hands server voedingen? Ik vind een meanwell toch wel iets te duur worden voor een zeer goedkope Frees.

Overigens vind ik de meanwells ook niet zo duur met ca 63 euro ex. btw voor 36V 300W: HRP-300-36

Ik kan zakelijk bestellen, echter dit is voor mijn prive werkplaats. De situatie die je daar ziet is wel ex. btw. Dus het wordt nog 21% duurder.base_ schreef op woensdag 26 september 2018 @ 14:24:

Servervoedingen zijn meestal 12V, je kan er drie in serie zetten als je de massa's losmaakt van de min.

Overigens vind ik de meanwells ook niet zo duur met ca 63 euro ex. btw voor 36V 300W: HRP-300-36

En ik heb liever een oude ATX voeding dan een nieuwe chinese tabletopvoeding met iffy specificaties...

[ Voor 22% gewijzigd door mcDavid op 26-09-2018 14:40 ]

Tja als je die niet goed belast (dus bv alleen de 5v lijn of alleen de 12v lijn) gaan die ook gewoon stukmcDavid schreef op woensdag 26 september 2018 @ 14:39:

Heb laatst hier uit de v&a twee tweedehands ATX voedingen gescoord om ledstrips te voeden. Compleet overkill natuurlijk, maarja wel bakken goedkoper dan wat dan ook wat je nieuw kunt kopen.

En ik heb liever een oude ATX voeding dan een nieuwe chinese tabletopvoeding met iffy specificaties...

Dat is probleem 1, en volgens mij hebben ATX voedingen niet eens 24V. Die hebben dacht ik een -12V en een + 12V maar dat kan je maar erg laag belasten volgens mij.sebastius schreef op woensdag 26 september 2018 @ 15:37:

[...]

Tja als je die niet goed belast (dus bv alleen de 5v lijn of alleen de 12v lijn) gaan die ook gewoon stuk

Vind je? https://www.tmart.com/S-4...Power-Supply_p380675.htmljctjepkema schreef op woensdag 26 september 2018 @ 14:18:

Bedrag is bijna te mooi om waar te zijn.

Ander ding, gelijke specs, gelijke prijs. Goed, ze zijn van chinesium gemaakt, maar als ze het doen, waarom ook niet?

I don't like facts. They have a liberal bias.

Waarom ook niet??burne schreef op woensdag 26 september 2018 @ 19:12:

[...]

Vind je? https://www.tmart.com/S-4...Power-Supply_p380675.html

Ander ding, gelijke specs, gelijke prijs. Goed, ze zijn van chinesium gemaakt, maar als ze het doen, waarom ook niet?

Omdat:

* Veiligheid voor jezelf

* Veiligheid voor de applicatie die ermee gevoed wordt

* Betrouwbaarheid/duurzaamhied

Het blijft natuurlijk ieders eigen keuze.

Persoonlijk heb ik genoeg chinese ontwerpen gezien om mezelf als regel te stellen: Geen chinese meuk kopen die op netspanning werkt.

Hmmz, hier komt dus m'n sig

Volgens mij geldt dat vooral als je veel vermogen op de 5V vraagt en geen op de 12V rails. Bij mij is het andersom, maak me daar dus niet zo druk om. Computers van tegenwoordig vragen sowieso nauwelijks vermogen op de 5V rails, dus je zou zeggen dat zo'n voeding daar mee om kan gaan. Zo niet dan merk ik het wel. Ik zie ze iig niet zo snel catastrofaal falen. Er wordt niets warm en er zitten nauwelijks brandbare materialen in. Dat is bij (zeker babi-pangang) tabletop-voedingen wel anders.sebastius schreef op woensdag 26 september 2018 @ 15:37:

[...]

Tja als je die niet goed belast (dus bv alleen de 5v lijn of alleen de 12v lijn) gaan die ook gewoon stuk

De -12 V is inderdaad alleen leuk voor signaalstroompjes. Je zou er meerdere in serie moeten hangen dan. Maar we zitten niet voor niets in de EL kroeg natuurlijkjctjepkema schreef op woensdag 26 september 2018 @ 18:52:

[...]

Dat is probleem 1, en volgens mij hebben ATX voedingen niet eens 24V. Die hebben dacht ik een -12V en een + 12V maar dat kan je maar erg laag belasten volgens mij.

Het ligt er voor mij een beetje aan wat het is en hoe ik het ga gebruiken. Voor dingen die onbeheerd in een stopcontact moeten kunnen blijven zitten ben ik bijvoorbeeld heel wat voorzichtiger dan voor hobbydingetjes die je alleen inprikt als je erbij bent.Gwannoes schreef op woensdag 26 september 2018 @ 19:31:

[...]

Waarom ook niet??

Omdat:

* Veiligheid voor jezelf

* Veiligheid voor de applicatie die ermee gevoed wordt

* Betrouwbaarheid/duurzaamhied

Het blijft natuurlijk ieders eigen keuze.

Persoonlijk heb ik genoeg chinese ontwerpen gezien om mezelf als regel te stellen: Geen chinese meuk kopen die op netspanning werkt.

Zijn gewoon HP DP600 en DP750 servervoedingen welke massaal voor een paar tientjes worden aangeboden. Deze persoon geeft ze een mooie wrap en doet een 3D geprint kapje over de aansluitingen.

Als je (toegang tot) een 3D printer hebt kan je zoiets ook voor andere voedingen doen.

Ik was vanavond even aan het hobbyen met een 2n7000 FET en een relais op een breadbordje. Gewoon dit simpele schema:

Ik zette de spanning er op en meteen sprong mijn voeding in de stroom begrenzer en de FET werd meer dan handwarm. Na wat zoeken bleek dat ik een Zender diode uit de la had gehaalt in plaats van een normale diode.

All electric components run on smoke. If you let the smoke out, they won't work anymore.

I´d rather be a hypocrite than the same person forever (Yauch)| 🎸 Niets is zo permanent als een tijdelijke oplossing | Een goed probleem komt nooit alleen | Gibson guitar Fender Guitar God Damn Guitar

Uiteraard, hij hangt nu aan een ESP. Werkt goed, zit er alleen aan te denken om er nog een 100k pulldown weerstand aan te hangen (tussen de ESP en de weerstand) puur om er voor te zorgen dat het relais uitblijft bij een reset.

All electric components run on smoke. If you let the smoke out, they won't work anymore.

Koop gewoon iets van Meanwell.

Degelijk merk en de prijzen zijn al super goed.

All electric components run on smoke. If you let the smoke out, they won't work anymore.

Van de mean well webshop:B_FORCE schreef op donderdag 27 september 2018 @ 12:15:

Snap de discussie niet helemaal over voedingen.

Koop gewoon iets van Meanwell.

Degelijk merk en de prijzen zijn al super goed.

Meanwell SP-480-24 - PSU enclosed 24V 22A

Artikelnummer SP-480-24

Specificaties: datasheet

Prijs € 132,03

I don't like facts. They have a liberal bias.

Mjah, mooie prijs toch voor 480W?

edit: ik lees net dat het maar rond de 300W hoeft.

Dan ben je voor iets van 70 euro klaar.

[ Voor 19% gewijzigd door B_FORCE op 27-09-2018 17:06 ]

Als je tijd geld kost zou ik er niet over nadenken en gelijk bestellen inderdaad. Maar voor de hobby is het toch weer 50 euro bespaard en nog een leuk projectje ook toch?

edit: Uhm, misschien mis ik iets, maar waar haal je ineens die "chinese troep" vandaan? We hadden het over re-purposed server- en ATX voedingen.

[ Voor 23% gewijzigd door mcDavid op 27-09-2018 17:21 ]

Je betaald (of bespaard) voor risico.mcDavid schreef op donderdag 27 september 2018 @ 17:11:

nouja als het ook voor 2 tientjes en wat handigheid kan, dan is 132 euro (of 70 for that matter) toch een tikkeltje duur.

Als je tijd geld kost zou ik er niet over nadenken en gelijk bestellen inderdaad. Maar voor de hobby is het toch weer 50 euro bespaard en nog een leuk projectje ook toch?

Ik heb al meerdere keren gehad dat zo'n Chinees ding er compleet uitklapte of zoveel troep terug op het net gooide dat het stoorde op andere apparatuur.

Maar goed, moet iedereen natuurlijk zelf weten.

Voor 50 tientjes tov het totaal lig ik nou niet heel erg wakker.

(nee ik heb geen geldboom)

Moet het zo goedkoop zijn, zou ik nog liever een oude trafo ergens vandaan plukken.

[ Voor 5% gewijzigd door B_FORCE op 27-09-2018 17:18 ]

Vrijwel alles wat je koopt is grotendeels in China gemaakt. Meanwell heeft ook fabrieken in Suzhou en Guangzhou. En zelfs de voedingen die ze in Taiwan assembleren zullen volzitten met weerstanden en condensators uit China.B_FORCE schreef op donderdag 27 september 2018 @ 17:17:

[...]

Ik heb al meerdere keren gehad dat zo'n Chinees ding er compleet uitklapte of zoveel troep terug op het net gooide dat het stoorde op andere apparatuur.

I don't like facts. They have a liberal bias.

Die voedingen zijn al voor 25 euro te vinden....

Maar wel aan te bevelen om op je spindel een softstart te maken om inschakelpiekstromen te voorkomen.

Je meent hetburne schreef op donderdag 27 september 2018 @ 17:47:

[...]

Vrijwel alles wat je koopt is grotendeels in China gemaakt. Meanwell heeft ook fabrieken in Suzhou en Guangzhou. En zelfs de voedingen die ze in Taiwan assembleren zullen volzitten met weerstanden en condensators uit China.

Dat is niet bepaald het punt als men zegt dat iets Chinees spul is.

Is ook gewoon een interessant onderwerp. Lang niet alle voedingen zijn goed en veilig. Zeker niet de goedkope meuk uit china. Voor sommige hobby zaken zijn is die china meuk echter prima denk ik. Andere mensen vinden de gemiddelde meanwell al slecht gebouwd

Die standaard 360 watt dingen ken ik van mijn 3D printer. Werkt tot nu toe prima @mux heeft zo'n ding volgens mij wel eens uit elkaar gehaald in een youtube video. Het was niet al te best, maar binnen de redelijk grote CR-10 community heb ik nog van niemand gehoord dat de voeding in de vik is gevlogen. Wel wat kapotte voedingen, maar allemaal op een veilige manier het leven gelaten.

Voor een nieuwe printerbesturing wou ik een low cost voeding hebben, die eventueel een beetje overgedimensioneerd mocht zijn.

Daarom van aliexpress een 480W voeding gekocht, maar de voeding inclusief PCB ziet er exact hetzelfde uit als de 360W versie. Ook zat er een linke klodder soldeer op de print, dus mijn geld teruggevraagd, en dat kreeg ik keurig terug.

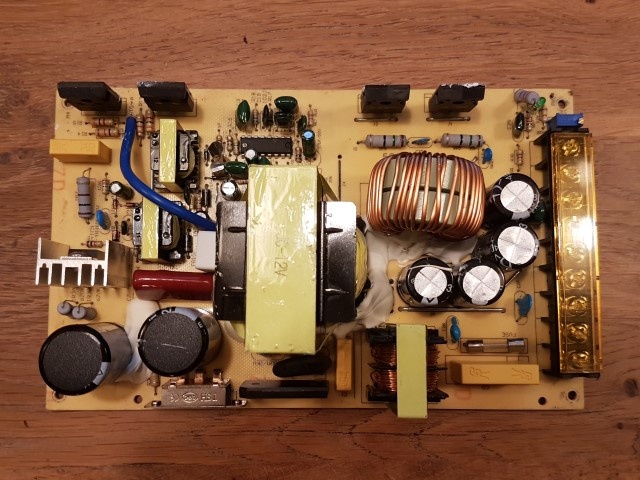

Toen maar een wat grotere 500W voeding besteld, en deze ziet er stukken beter uit. Meer koeling, meer halfgeleiders, meer trafo's. Ik heb mijn analoge electronica kennis en PCB ontwerp kunsten nooit ver genoeg ontwikkeld om het ontwerp echt goed te kunnen beoordelen, maar ik vindt het er een stuk degelijker uit zien dan de kleinere 360/480W voeding.

Mocht mux of een andere pro deze de zwaardere voeding een keer willen testen, wil ik deze wel beschikbaar stellen!

Meer foto's in high-res hieerrrr.....

Dan regel je toch voor een paar tientjes die servervoedingen: de meest geschikte zijn de hot-swappables die zo'n beetje alle stroom op de 12V leveren, dus voor jouw 36V heb je er precies drie nodig. Ze beginnen bij 350W per stuk dus met 1000W totaal moet dt prima voldoen! Vergeet niet de gehele massa te scheiden van de secundaire kant, dat kan voor sommige modellen een uitdaging zijn. Ik neem aan dat het overbodig is om te vermelden dat de 400VDC in de caps aan de primaire zijde ook na uitschakelen best pijnlijk zijnmcDavid schreef op donderdag 27 september 2018 @ 17:11:

nouja als het ook voor 2 tientjes en wat handigheid kan, dan is 132 euro (of 70 for that matter) toch een tikkeltje duur.

Let wel op dat bij eventuele brandschade de verzekering best moeilijk kan doen over gemodificeerde voedingen.

edit: @jctjepkema : Neem dit niet te persoonlijk op maar het feit dat je hier vraagt of er nog goedkopere (63 euro ex btw/verz voor een betrouwbare meanwell??) mogelijkheden zijn geeft mij weinig vertrouwen.

Ze worden heel erg veel gebruikt in productie van diverse bedrijven vanwege de gunstige prijs.

Ik zou best zelf een SMPS kunnen ontwikkelen (in het verleden ook wel gedaan), maar why bother voor 50-70 euro?

Hoewel ik het avontuur en de uitdaging snap om nog iets goedkopers te vinden, is er op een gegeven moment een bepaald minimum bereikt.

Sommige mensen willen voor een dubbeltje op de eerste rij zitten.

Volgens mij moet je de discussie nog eens teruglezen, want ik heb echt géén idee waarom je mij aanspreekt hiermee.base_ schreef op zaterdag 29 september 2018 @ 01:59:

[...]

Dan regel je toch voor een paar tientjes die servervoedingen: de meest geschikte zijn de hot-swappables die zo'n beetje alle stroom op de 12V leveren, dus voor jouw 36V heb je er precies drie nodig. Ze beginnen bij 350W per stuk dus met 1000W totaal moet dt prima voldoen! Vergeet niet de gehele massa te scheiden van de secundaire kant, dat kan voor sommige modellen een uitdaging zijn. Ik neem aan dat het overbodig is om te vermelden dat de 400VDC in de caps aan de primaire zijde ook na uitschakelen best pijnlijk zijn

Let wel op dat bij eventuele brandschade de verzekering best moeilijk kan doen over gemodificeerde voedingen.

Neem dit niet te persoonlijk op maar het feit dat je hier vraagt of er nog goedkopere (63 euro ex btw/verz voor een betrouwbare meanwell??) mogelijkheden zijn geeft mij weinig vertrouwen.

/u/4024/burne.png?f=community)

:strip_icc():strip_exif()/u/42559/crop68b894d172ae2_cropped.jpg?f=community)

/u/76904/crop5735f86b5a875.png?f=community)

:strip_icc():strip_exif()/u/407197/tweakers%2520forum.jpg?f=community)

:strip_icc():strip_exif()/u/109773/ziltoid_fetid_70px.jpg?f=community)

/u/238475/crop5db01b7054bdf_cropped.png?f=community)

:strip_exif()/u/58926/max5885.gif?f=community)

:strip_icc():strip_exif()/u/145321/dirkjan.jpg?f=community)

:strip_icc():strip_exif()/u/94119/358157.jpg?f=community)

:strip_exif()/u/128173/crop59a1592e54731_cropped.gif?f=community)

:strip_icc():strip_exif()/u/510323/crop5c49c55cb1a09_cropped.jpeg?f=community)

/u/394945/Usadasdntitled.png?f=community)

:strip_icc():strip_exif()/u/338322/crop65815b314a173.jpg?f=community)

:strip_icc():strip_exif()/u/31456/Marineblauw.jpg?f=community)

:strip_icc():strip_exif()/u/92491/crop64a1593f33a7b_cropped.jpg?f=community)

:strip_exif()/u/112988/knipper.gif?f=community)

:strip_icc():strip_exif()/u/390179/WP_20140716_11_23_49_Pro.jpg?f=community)

:strip_icc():strip_exif()/u/117376/smile%2520klein.jpg?f=community)

:strip_exif()/u/259931/stuiterbal2.gif?f=community)

:strip_exif()/u/12601/cat_matrix2.gif?f=community)

:strip_exif()/u/3157/sail4L_S70.gif?f=community)

:strip_icc():strip_exif()/u/362053/crop58aad0d9b6b17_cropped.jpeg?f=community)